脉异步时序电路的设计步骤基本上与同步时序电路的设计步骤一样。但须特别考虑:

⑴ 输入信号 x 及触发器的时钟信号 CLK 取值为:

0—无脉冲 1—有脉冲

⑵ 采用简化的状态表和状态图。

⑶ 在确定控制函数时,不仅要确定各触发器的控制输入信号,而且还需确定各触发器的时钟信号。

?时钟信号 CLK 应是现态 Qn及输入 x 的函数.

?各触发器的输入控制信号 X应尽量使其仅为现态Qn 的函数,

这样使其具有保证电路正常工作所需的建立和保持时间。

⑷ 状态不变时,令 CLK = 0,这样触发器的数据端变量就可认为是无关最小项d ,这有利于函数的化简

例1 用D触发器设计一个“x1 – x1 – x2 ”序列检测器。

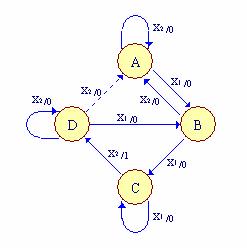

⑴ 建立原始状态图和状态表如图1所示。

图1 状态图

表

例1 状态表

|

yn+1/Z |

X1 |

X2 |

|

A |

B/0 |

A/0 |

|

B |

C/0 |

A/0 |

|

C |

C/0 |

D/1 |

|

D |

B/0 |

D/0 |

⑵ 状态化简

从原始状态表中可明显看到A、D等效, AD合并后可得到最小化状态表。

|

|

X1 |

X2 |

|

A |

B/0 |

A/0 |

|

B |

C/0 |

A/0 |

|

C |

C/0 |

A/1 |

⑶ 状态分配

|

yn+1/Z |

X1 |

X2 |

|

00 |

01/0 |

00/0 |

|

01 |

11/0 |

00/0 |

|

11 |

11/0 |

00/1 |

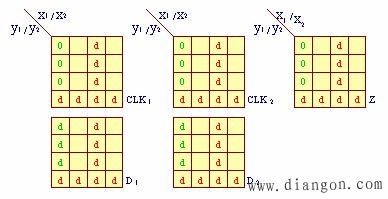

⑷ 确定控制函数及输出函数

① 作出 CLK1、D1 、 CLK2、D2 的卡诺图.

|

|

X1 |

X2 |

|

00 |

01/0 |

00/0 |

|

01 |

11/0 |

00/0 |

|

11 |

11/0 |

00/1 |

|

10 |

dd/d |

dd/d |

在y1y2 = 10 时,若 x2 = 1时, 有一个错误的输出 1

因此修改输出函数表达式:

Z = x2y1y2

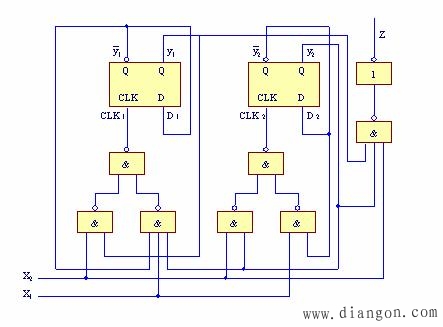

(5)画出电路图

图2 例1的电路图