必须满足二进制加法原则:逢二进一(1+1=10,即Q由1加1→0时有进位);各触发器应满足两个条件:每当CP有效触发沿到来时,触发器翻转一次,即用T′触发器。 控制触发器的CP端,只有当低位触发器Q由1→0(下降沿)时,应向高位CP端输出一个进位信号(有效触发沿),高位触发器翻转,计数加1。由JK触发器组成4位异步二进制加法计数器。

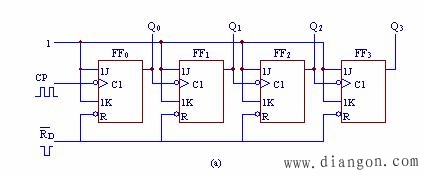

① 逻辑电路

JK触发器都接成T′触发器,下降沿触发。

图1 由JK触发器组成的4位异步二进制加法计数器

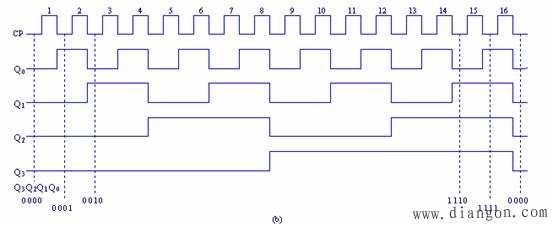

(a)逻辑图;(b)工作波形

② 工作原理

异步置0端![]() 上加负脉冲,各触发器都为0状态,即Q3Q2Q1Q0=0000状态。在计数过程中,

上加负脉冲,各触发器都为0状态,即Q3Q2Q1Q0=0000状态。在计数过程中, ![]() 为高电平。只要低位触发器由1状态翻到0状态,相邻高位触发器接收到有效CP触发沿, T′的状态便翻转。

为高电平。只要低位触发器由1状态翻到0状态,相邻高位触发器接收到有效CP触发沿, T′的状态便翻转。

③ 状态转换顺序表如下表所示。

电路为十六进制计数器。

④ 工作波形(又称时序图或时序波形)如图1所示.

输入的计数脉冲每经一级触发器,其周期增加一倍,即频率降低一半。

一位二进制计数器就是一个2分频器,

16进制计数器即是一个16分频器。

四位二进制加法计数器 状态转换顺序表:

|

计数顺序 |

计 数 器 状 态 |

|

Q3 Q2 Q1 Q0 | |

|

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 0 0 0 |

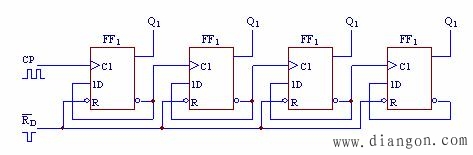

图2为由D触发器组成的4位异步二进制加法计数器的逻辑图。

由于D触发器用输入脉冲的上升沿触发,因此,每个触发器的进位信号由 ![]() 端输出。

端输出。

其工作原理与上类似。

图2 由D触发器组成的4位异步二进制加法计数器