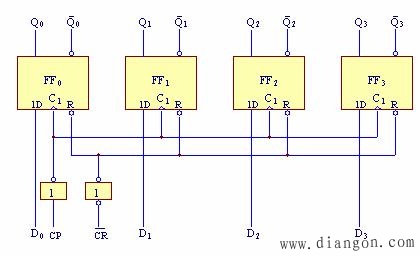

由维持阻塞D触发器组成的4位代码寄存器逻辑电路图如图所示。

CR是异步置0输入端(低电平有效) D0~D3为并行数码输入端,

CP为时钟脉冲 Q0~Q3为并行数码输出端

图 4位代码寄存器逻辑图

逻辑功能分析:

①异步置0端CR=0时,置0。

②同步并行置数:D0~D3为4个输入数码,当CP上升沿到达时,D0~D3被并行置入,

Q3 Q2 Q1 Q0=D3D2 D1D 0

③在CR=1,CP=0时,保持不变。

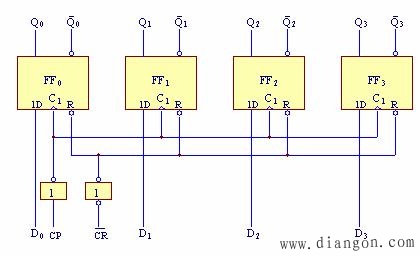

由维持阻塞D触发器组成的4位代码寄存器逻辑电路图如图所示。

CR是异步置0输入端(低电平有效) D0~D3为并行数码输入端,

CP为时钟脉冲 Q0~Q3为并行数码输出端

逻辑功能分析:

①异步置0端CR=0时,置0。

②同步并行置数:D0~D3为4个输入数码,当CP上升沿到达时,D0~D3被并行置入,

Q3 Q2 Q1 Q0=D3D2 D1D 0

③在CR=1,CP=0时,保持不变。

下一篇异步十进制加法计数器