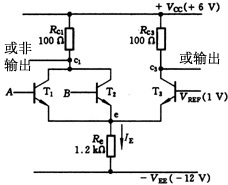

图1是最简单的ECL门,硅BJT T1、T2、T3组成发射极耦合电路。T3的基极接一个固定的参考电压VREF,输入信号接到T1、T2的基极。输出信号由T1、T2或T3的集电极取得。

|

图1 ECL门基本电路 |

由于VREF=1V,因此T3优先导通,这就使发射极e的电位VE=VREF-VBE3=0.3V。对于T1、T2来说,由于 VE=0.3V,而VA=VB=0.5V,虽然基极电位比发射极电位高0.2V,但由于是硅管,仍可保证截止。这时流过Re的电流将全部由T3提供,且有IE=[VE-(-VEE)]/Re=(0.3V+12V)/1.2KΩ≈10mA。这样

| VC3=VCC-IERc3=6V-10mA×0.1KΩ=5V |

| 而 | VC1=VCC=6V |

2.当输入端A、B中有一个接高电平1(设A接高电平,VA=1.5V)时

由于VA>VREF,所以T1优先导通,这就使VE=1.5V-0.7V=0.8V,对T3来说,这时基极电位比发射极电位仅高0.2V,可以保证T3截止。流过Re的电流由T1提供,且有IE=(0.8V+12V)/1.2 KΩ=10.6mA,而

| VC1=VCC-IERc1=6V-10.6mA×0.1KΩ≈5V |

| VC3=VCC=6V |

由上分析可得

| c1=A+B 或非输出 |

| c3=A+B 或输出 |

同时,不论是哪个BJT导通,所形成的发射极电流IE都是很接近的。这个电流受输入信号控制,分别流入T1或T2或T3,就象一个开关在控制,所以ECL电路又称为电流开关型电路(CML)。

以上所述的是具有A、B两个输入端的或非电路,只要增加相同类型的BJT与T1并联,就能增加门电路的输入端数。

图1所示电路中存在的问题是,输出端的高、低电平与输入端的高、低电平电压不一致(尽管摆幅相等)如表1所示。实用上,可采用加电压跟随器等移动电平值的措施来解决。

| 表1ECL门输入输出电平对照表 |

| 输入 | 输出 | ||

| 低电平0 | 高电平1 | 低电平0 | 高电平1 |

| +0.5V | +1.5V | +5V | +6V |