来源:本站

导读:目前正在解读《TTL与非门的技术参数》的相关信息,《TTL与非门的技术参数》是由用户自行发布的知识型内容!下面请观看由(

电工学习网 - www.9pbb.com)用户发布《TTL与非门的技术参数》的详细说明。

1.输入和输出的高、低电平

|

输出高电平VOH≈VO(A)=3.6V |

|

输出低电平VOL=VCES=0.2V |

|

输入低电平VIL=VI(B)=0.4V |

|

输入高电平VIH=VI(D)=1.2V |

由于不同类型TTL器件,其vI-vo特性各不相同,因而其输入和输出高、低电平也各异。

2.噪声容限

|

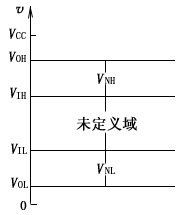

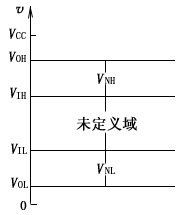

噪声容限表示门电路的抗干扰能力。二值数字逻辑电路的优点在于它的输入信号允许一定容差。反相器的传输特性中的输入、输出高、低电平绘制成图1所示,由此图可知,高电平(逻辑1)所对应的电压范围(VIH~VOH)和低电平(逻辑0)所对应的电压范围(VOL~VIL)分别称之为高、低电平的噪声容限,用符号VNH和VNL表示:

|

VNH=VOH-VIH |

VNL=VIL-VOL

|

图1噪声容限的图解

3.扇入与扇出数

(1)扇入数:TTL门电路的输入端的个数,例如一个3输入端的与非门,其扇入数Ni=3。

(2)扇出数:以TTL与非门带同类门作为负载时来讨论,有两种情况,一种情况是负载电流从外电路流入与非门,称为灌电流负载;另一种是负载电流从与非门流向外电路,称为拉电流负载。

①灌电流工作情况

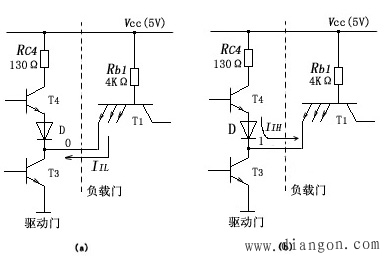

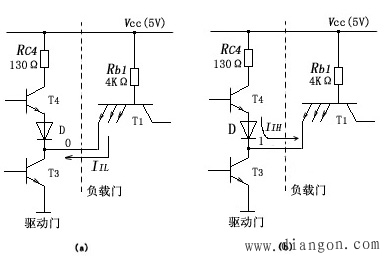

图2与非门的带负载能力(a)灌电流负载(b)拉电流负载

图2(a)表示TTL与非门的灌电流负载的情况。图中左边为驱动门,右边为负载门,当驱动门的输出端为逻辑0(低电平VOL)时,负载门由电源Vcc通过Rb1、T1的发射结和输入端有电流IIL灌入驱动门的T3集电极,这就是灌电流负载。当负载门的个数增加时,总的灌电流IIL将增加,同时也将引起输出低电平VOL的升高。因为,TTL门电路的标准输出低电平VOL=0.4V,这就限制了负载门的个数。在输出为低电平的情况下,所能驱动的同类门的个数由下式决定:

②拉电流工作情况

当驱动门的输出为高电平时,将有电流IIH从驱动门拉出而流至负载门。当负载门的个数增多时,必将引起输出高电平的降低,但不得低于标准高电平的低限值VIH=2V。这样,输出为高电平时的扇出数可表示如下:

通常基本的TTL门电路,其扇出数约为10,而性能更好的门电路的扇出数最高可达30~50。

|

4. 传输延迟时间

传输延迟时间是表示门电路开关速度的参数,它表示门电路在输入脉冲波形的作用下,其输出波形相对于输入波形延迟了多长的时间。

5. 功耗

功耗包括静态功耗和动态功耗。所谓静态功耗指的是当电路没有状态转换时的功耗,即与非门空载时电源总电流ICC与电源电压VCC的乘积。输出为低电平时的功耗称为空载导通功耗PON;输出为高电平时的功耗称为截止功耗POOF,PON总比POOF大。动态功耗只发生在状态转换的瞬间,或者电路中有电容性负载时,例如TTL门电路约有5pF的输入电容,由于电容的充、放电过程,将增加电路的损耗。

6. 延时—功耗积

理想的数字电路或系统,要求它既具有高速度,同时功耗又低。在工程实践中,要实现这种理想情况是较难的。高速数字电路往往需要付出较大的功耗为代价。一种综合性的指标叫做延时—功耗积,用符号DP表示,单位为焦耳,即

式中tpd=(tPLH+tPHL)/2,PD为门电路的功耗,一个逻辑门器件的DP值愈小,表明它的特性愈接近于理想情况。

提醒:《TTL与非门的技术参数》最后刷新时间 2023-07-10 03:58:12,本站为公益型个人网站,仅供个人学习和记录信息,不进行任何商业性质的盈利。如果内容、图片资源失效或内容涉及侵权,请反馈至,我们会及时处理。本站只保证内容的可读性,无法保证真实性,《TTL与非门的技术参数》该内容的真实性请自行鉴别。