来源:本站

导读:目前正在解读《组合逻辑电路中的竞争冒险》的相关信息,《组合逻辑电路中的竞争冒险》是由用户自行发布的知识型内容!下面请观看由(

电工学习网 - www.9pbb.com)用户发布《组合逻辑电路中的竞争冒险》的详细说明。

实际上,信号通过连线及集成门都有一定的延迟时间,也可能有前后快慢的差异。由于从输入到输出的过程中,不同通路上门的级数不同,或者门电路平均延迟时间的差异,使信号从输入经不同通路传输到输出级的时间不同。受到上面因素的影响后,可能在输入信号变化的瞬间,在输入端出现一些不正确的尖峰信号输出,通常把这种现象称为竞争冒险。

1、产生竞争冒险的原因

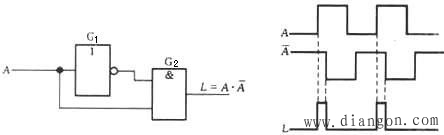

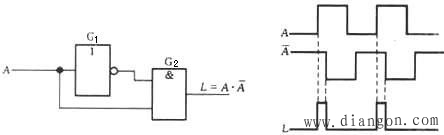

首先来分析图1所示电路的工作情况,以建立竞争冒险的概念。在图1(a)中,与门G2的输入是A和A两个互补信号。由于G1的延迟,A的下降沿要滞后于A的上升沿,因此在很短的时间间隔内,G2的两个输入端都会出现高电平,致使它的输出出现一个高电平脉冲(它是按逻辑设计要求不应出现的干扰脉冲),如图1(b)所示。与门G2的2个输入信号分别由G1和A端的两个路径在不同的时刻到达的现象,通常称为竞争,由此而产生输出干扰脉冲的现象称为冒险。

(a)逻辑电路(b)工作波形

图1 产生正跳变脉冲的竞争冒险

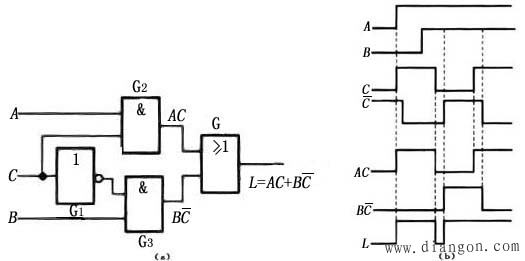

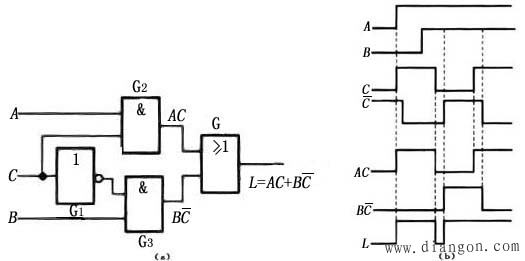

下面进一步分析组合逻辑电路产生竞争冒险的原因。设有一个逻辑电路如图2(a)所示,其工作波形如图2(b)所示。它的输出逻辑表达式为L=AC+BC。由此式可知,当A和B都为1时,L=1,与C的状态无关。但是,由图2(b)可以看出,在C由1变0时,C由0变1有一延迟时间,在这个时间间隔内,G0和G3的输出AC 和BC 同时为0,而使输出出现一负跳变的窄脉冲,即冒险现象。这是产生竞争冒险的原因之一。由以上分析可知,当电路中存在由反相器产生的互补信号,且在互补信号的状态发生变化时可能出现冒险现象。

图2 产生负跳变脉冲的竞争冒险 (a)逻辑电路 (b)工作波形

图2 产生负跳变脉冲的竞争冒险 (a)逻辑电路 (b)工作波形

|

2、消除竞争冒险的方法

针对上述原因,可以采取以下措施消除竞争冒险现象。

1. 发现并消掉互补变量

例如,函数式F=(A+B)(A+C),在B=C=0时,F=AA。若直接根据这个逻辑表达式组成逻辑电路,则可能出现竞争冒险。可以将该式变换为F=AC+AB+BC,这里已将AA消掉。根据这个表达式组成逻辑电路就不会出现竞争冒险。

2. 增加乘积项

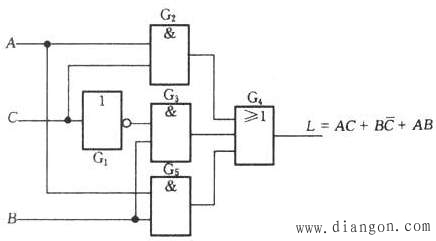

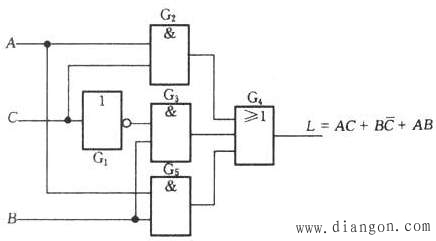

对于图2(a)所示的逻辑电路,可以根据以前所介绍的常用恒等式,在其输出逻辑表达式中增加乘积项AB。这时,L=AC+BC+AB,对应的逻辑电路如图3所示。由图2(b)可以看出,出现负跳变窄脉冲处,正是A和B均为1时。显然,对于图3所示电路,当A=B=1时,G5输出为1,G4输出亦为1,这就消除了C 跳变时对输出状态的影响,从而消除了竞争冒险。

图3 增加了乘积项AB的逻辑电路 |

|

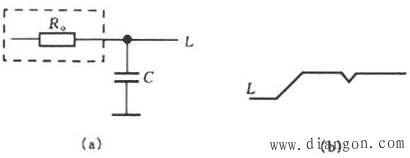

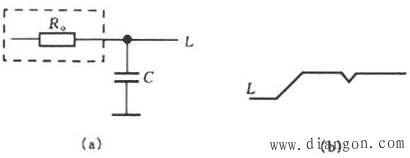

3.输出端并联电路

如果逻辑电路在较慢速度下工作,为消除竞争冒险,可以在输出端并联一电容器,其容量为4~20pF之间。如图4(a)所示,即在图2(a)所示电路的输出端并联电容C。由于或门G4存在一输出电阻R0,致使输出波形上升沿和下降沿变化比较缓慢。因此对于很窄的负跳变脉冲起到平波的作用,如图4(b)所示。显然,这时在输出端不会出现逻辑错误。

以上介绍了产生竞争冒险的原理和克服竞争冒险的方法。要能很好地解决这一问题,还必须在实践中积累和总结经验。

图4 并联电容器消除竞争冒险 (a)电路 (b)输出波形 |

提醒:《组合逻辑电路中的竞争冒险》最后刷新时间 2023-07-10 03:57:11,本站为公益型个人网站,仅供个人学习和记录信息,不进行任何商业性质的盈利。如果内容、图片资源失效或内容涉及侵权,请反馈至,我们会及时处理。本站只保证内容的可读性,无法保证真实性,《组合逻辑电路中的竞争冒险》该内容的真实性请自行鉴别。

图2 产生负跳变脉冲的竞争冒险 (a)逻辑电路 (b)工作波形

图2 产生负跳变脉冲的竞争冒险 (a)逻辑电路 (b)工作波形