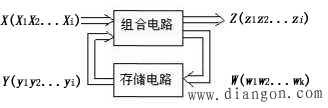

X(x1,x2…xi)为外部输入信号;

Z(z1,z2…zj)为电路的输出信号;

W(w1,w2…wk)为存储电路的输入;

Y(y1,y2…yl)为存储电路的输出,也是组合逻辑电路的部分输入。

这些信号之间的关系为:

Z(tn)=F[X(tn),Y(tn)];

W(tn)=G[X(tn),Y(tn)];

Y(tn+1)=H[W(tn),Y(tn)],

其中Y(tn)表示tn时刻存储电路的当前状态(现态)。Y(tn+1)表示存储电路的下一个状态(次态)。由这些状态可以看出,tn+1时刻的输出Z(tn+1)是由tn+1时刻的输入X(tn+1)及存储电路在tn+1时刻的状态Y(tn+1)决定;而Y(tn+1)又由tn时刻的存储电路的激励(驱动)输入W(tn)及在tn时刻存储电路的状态Y(tn)决定。因此,tn+1时刻电路的输入不仅决定于tn+1时刻的输入

X(tn+1),而且还决定于在tn时刻存储电路的输入W(tn)及存储电路在tn时刻的状态Y(tn),这充分反映了时序逻辑电路具有如下特点:

1.功能上:电路的输出状态不仅与即刻输入变量的状态有关,而且还与系统原先的状态有关。

2.结构上:由组合电路和存储电路(记忆单元)组成,其中存储电路一般由触发器构成。

|

| 图1时序电路的结构框图 |