常用时序逻辑电路有计数器和寄存器两种。寄存器分为数据寄存器和移位寄存器。计数器种类较多,有同步计数器、异步计数器;有二进制计数器、十进制计数器、任意进制计数器;二进制计数器又有加法计数器、减法计数器等。

(1)寄存器

数字电路中用来存放数码或指令的部件称为寄存器。寄存器具有以下逻辑功能:可在时钟脉冲作用下将数码或指令存入寄存器(称为写入),或从寄存器中将数码或指令取出(称为读出)。由于一个触发器只能寄存1位二进制数,要存多位数时,就得用多个触发器。常用的有4位、8位、16位等。

寄存器存放和取出数码的方式有并行和串行两种。并行方式就是数码各位同时从各对应位输入端输入到寄存器中,或同时出现在输出端;串行方式就是数码逐位从一个输入端输入到寄存器中,或由一个输出端输出。

寄存器根据功能的不同可分为数码寄存器和移位寄存器两种。

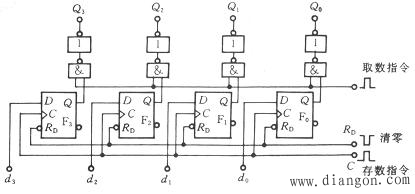

(a)数码寄存器:这种寄存器只有寄存数码和清除数码的功能。图1所示是由D触发器组成的4位数码寄存器。该数码寄存器的工作方式为并行输入、并行输出。

图1 4位数码寄存器

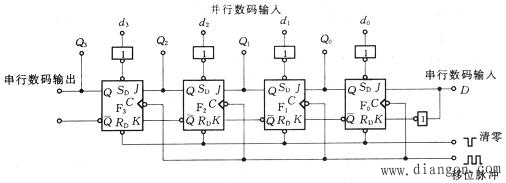

(b)移位寄存器:移位寄存器不仅能存放数码而且有移位功能。根据数码在寄存器内移动的方向又可分为左移移位寄存器和右移移位寄存器两种。

在移位寄存器中,数码的存入或取出也有并行和串行两种方式。

图2所示是由J—K触发器组成的4位左移移位寄存器。F0接成D触发器,数码由D端串行输入;也可由d0~d3作并行输入。从4个触发器的Q端得到并行的数码输出。也可从Q3端逐位串行输出。

图2 4位左移移位寄存器

(2)计数器

因为计数器是最常用而又典型的时序逻辑电路,其分析方法即为一般时序逻辑电路的分析方法。常用计数器有多种类型,重点掌握以下几种。

①二进制计数器:二进制计数器能按二进制的规律累计脉冲的数目,也是构成其它进制计数器的基础。一个触发器可以表示l位二进制数,表示n位二进制数就得用n个触发器。

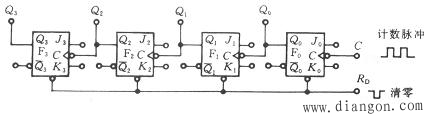

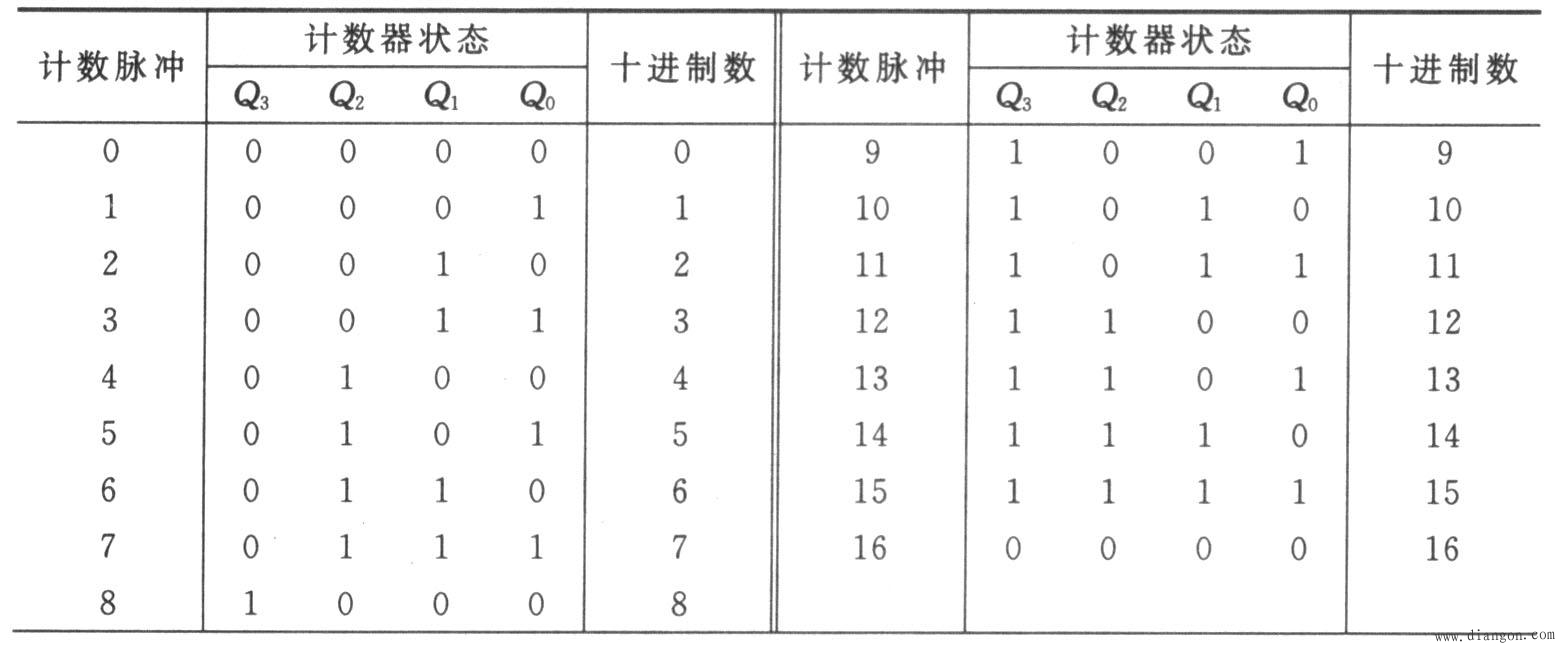

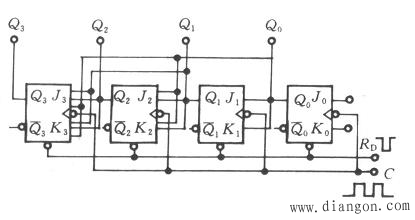

(a)异步二进制加法计数器:图3所示逻辑电路是由4个J—K触发器组成的4位异步二进制加法计数器。图中各触发器输入端均为“1”(悬空)即计数状态。只要有时钟脉冲就会翻转,但前级触发器的输出作为后级触发器的时钟脉冲,只有在前级触发器翻转后,后级触发器才能翻转,故为异步计数器。其状态真值表见图4。

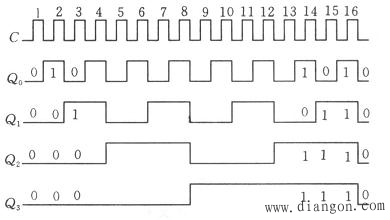

可见,在第16个时钟脉冲到来后,计数器循环一周回到原态,因此也称为十六进制计数器。其波形图如图5所示,由图可知,各触发器输出端Q0,Q1,Q2,Q3的脉冲频率分别为时钟脉冲的1/2,l/4,l/8,1/16,也称分频器。

图3 4位异步二进制加法计数器

图4异步计数器状态真值表

图5 十六进制计数器波形图

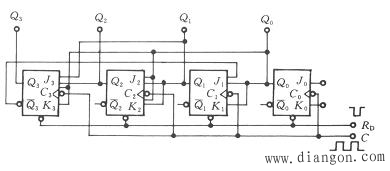

(b)同步二进制加法计数器:异步二进制计数器线路简单,工作速度较慢。同步计数器工作速度较快,电路较复杂。图6所示为同步4位二进制加法计数器的逻辑电路图。从图中可以看出计数脉冲同时供给各触发器,它们的状态变换和计数脉冲同步。图中每个触发器有多个J端和K端,各J端或各K端之间都是“与”逻辑关系。

各触发器输入端的逻辑表达式(驱动方程)为

J0=K0=1

J1=K1=Q0

J2=K2=Q1Q0

J3=K3=Q2Q1Q0

该计数器的状态表和波形图与异步4位二进制加法计数器相同。分析可知,n位二进制加法计数器能计的最大十进制数为2n-1。

图6 同步4位二进制加法计数器的逻辑电路图

②十进制计数器:从4位二进制数码的16种状态中任取10种状态,来表示1位十进制数,可有多种组合,也称编码。常用的编码形式是8421加权码,相应的计数器称8421十进制计数器。图7所为同步十进制加法计数器。

图7 同步十进制加法计数器

③集成计数器:将多个触发器构成的计数器做在一块中规模芯片上构成集成计数器,用它可构成所需模数的各种计数器。

④用中规模集成计数器组成任意进制计数器,通常有两种方法:

(a)反馈复位法(或称反馈“清0”法):它是利用中规模组件进行正常计数,当计数器达到N进制进位要求时,形成复位脉冲,并用此脉冲反馈到组件的异步复位(/![]() )端,使计数器复位(“清0”),实现N进制计数功能。

)端,使计数器复位(“清0”),实现N进制计数功能。

(b)反馈置数法(或称反馈预置法):根据74LSl6l等通用计数器的功能,可将任意状态译码后反馈到置数命令端(![]() ),并在下一个脉冲时给计数器并行输入0000~1111之间的任意一个状态,从而实现任意计数方法的N进制计数器。例如当计数器计到1001时发出反馈信号给

),并在下一个脉冲时给计数器并行输入0000~1111之间的任意一个状态,从而实现任意计数方法的N进制计数器。例如当计数器计到1001时发出反馈信号给![]() ,下一个脉冲将计数器置成0100,于是计数器便成为六进制计数器,其状态由0100到1001循环变化。这种方法称反馈预置法。

,下一个脉冲将计数器置成0100,于是计数器便成为六进制计数器,其状态由0100到1001循环变化。这种方法称反馈预置法。