时序电路设计又称为时序电路综合,它是时序电路分析的逆过程,即根据给定的逻辑功能要求,选择适当的逻辑器件,设计出符合要求的时序逻辑电路。本文介绍用触发器及门电路设计同步时序逻辑电路的方法,这种设计方法的基本指导思想是使用尽可能少的时钟触发器和门电路来实现待设计的时序电路。

设计同步时序电路的一般过程如图1所示。

|

|

| 图1 同步时序电路的设计过程 |

1.由给定的逻辑功能求出原始状态图

由于时序电路在某一时刻的输出信号,不仅与当时的输入信号有关,而且还与电路原来的状态有关。因此设计时序电路时,首先必须分析给定的逻辑功能,从而求出对应的状态转换图。这种直接由要求实现的逻辑功能求得的状态转换图叫做原始状态图。正确画出原始状态图,是设计时序电路的最关键的一步,具体的做法是:

(1)分析给定的逻辑功能,确定输入变量,输出变量及该电路应包含的状态,并用字母S0、S1…表示这些状态。

(2)分别以上述状态为现态,考察在每一个可能的输入组合作用下应转到哪个状态及相应的输出,便可求得符合题意的状态图。

2.状态化简

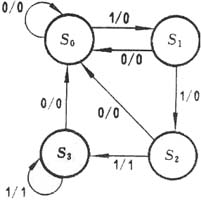

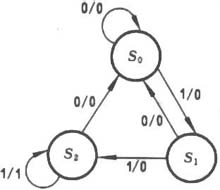

根据给定要求得到的原始状态图不一定是最简的,很可能包含多余的状态,即可以合并的状态,因此需要进行状态化简或状态合并。状态化简是建立在状态等价这个概念的基础上的。所谓状态等价,是指在原始状态图中,如果有两个或两个以上的状态,在输入相同的条件下,不仅有相同的输出,而且向同一个次态转换,则称这些状态是等价的。凡是等价状态都可以合并。如图2中的状态S2和S3,当输入X=0时,输出Z都是0,且都向同一个次态S0转换;当X=1时,输出Z都是1,次态都是S3,所以S2和S3是等价状态,可以合并为S2,取消S3,即将图2中代表S3的圆圈及由该圆圈出发的所有连线去掉,将原先指向S3的连线改而指向S2,得到化简后的状态图如图9.1.3所示。 显然,状态化简使状态数目减少,从而可以减少电路中所需要触发器的个数和门电路的个数。

|

|

| 图2原始状态图 | 图3图2的简化状态图 |

在得到简化的状态图后,要对每一个状态指定一个二进制代码,这就是状态编码(或称状态分配)。编码的方案不同,设计的电路结构也就不同。编码方案选择得当,设计结果可以很简单。为此,选取的编码方案应该有利于所选触发器的驱动方程及电路输出方程的简化。为了便于记忆和识别,一般选用的状态编码都遵循一定的规律,如用自然二进制码。编码方案确定后,根据简化的状态图,画出编码形式的状态图及状态表。

4.选择触发器的类型及个数

按照下式选择触发器的个数n

| 2n-1<M≤2n |

5.求电路的输出方程及各触发器的驱动方程

根据编码后的状态表及触发器的驱动表可求得电路的输出方程和各触发器的驱动方程。

6.画逻辑电路图,并检查自启动能力