来源:本站

导读:目前正在解读《由主从JK触发器组成的8421码异步五进制计数器》的相关信息,《由主从JK触发器组成的8421码异步五进制计数器》是由用户自行发布的知识型内容!下面请观看由(

电工学习网 - www.9pbb.com)用户发布《由主从JK触发器组成的8421码异步五进制计数器》的详细说明。

例1 试设计一个由主从JK触发器组成的8421码异步五进制计数器。

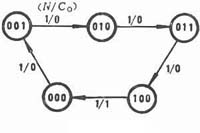

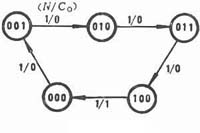

解:1. 作状态图。由于已经明确该计数器的编码为8421码,因此可直接作出如图1所示的状态图。输入

N 为计数脉冲,

CO为进位输出信号。

|

|

图1 例1的状态图 |

2.由于该题不必再对状态进行化简,且触发器的类型和状态编码都是已知的,因此可直接根据状态图列激励表(含CP变量)。在确定J、K 和CP 信号的状态(有无CP脉冲加入)时要综合考虑,其原则是:

(1)触发器状态需要改变时必须加入时钟脉冲;

(2)兼顾各J、K 和CP 端逻辑表达式的简化。无输入脉冲CP 时(CP =0),触发器不翻转,这时J、K 可取任意逻辑常量,即可作为无关项。无关项增加,有利于J、K 表达式的化简,但是CP =0项的增加,又可能不利于CP 表达式的化简。总之,如果选用多输入端的JK 触发器,那么应尽可能使计数器电路只由触发器组成,而不附加门电路。根据上述原则列出异步五进制计数器的激励表,如表1所示。

|

表1 异步五进制计数器激励表 |

|

现态 |

J、K与CP |

次态 |

|

Q2n |

Q1n |

Q0n |

J2 |

K2 |

CP2 |

J1 |

K1 |

CP1 |

J0 |

K0 |

CP0 |

CO |

Q2n+1 |

Q1n+1 |

Q0n+1 |

|

0 |

0 |

0 |

0 |

× |

1 |

× |

× |

0 |

1 |

× |

1 |

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

× |

1 |

1 |

× |

1 |

× |

1 |

1 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

× |

1 |

× |

× |

0 |

1 |

× |

1 |

0 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

× |

1 |

× |

1 |

1 |

× |

1 |

1 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

× |

1 |

1 |

× |

× |

0 |

0 |

× |

1 |

1 |

0 |

0 |

0 | |

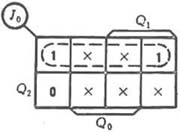

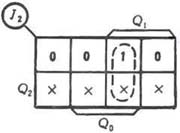

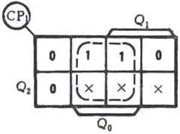

3.作各J、K 和CP 函数的卡诺图,并进行化简。由表9.3.1可直接看出CP0、CP2、K0、J1、K1和K2都为1,CO=Q2。做出J0、J2和CP1的卡诺图,如图2所示,由卡诺图化简得

J0=Q2 J2=Q1Q0 CP1=Q0

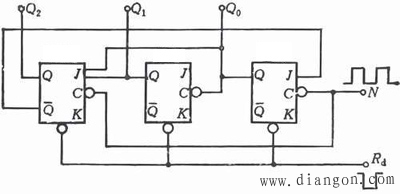

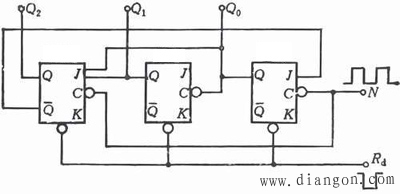

根据以上逻辑表达式画出逻辑图,如图3所示。CP=1,表示CP端直接与计数输入脉冲相连。

|

|

|

|

图3 异步五进制递增计数器的逻辑图 |

综上所述,对时序逻辑电路的分析与设计可归纳如下几点:

1.作状态图和列状态表是分析与设计时序逻辑电路的重要步骤。

2.分析过程是,从电路写出输出逻辑表达式、驱动方程和状态方程,在此基础上作出状态图或列出状态表,然后总结电路的逻辑功能和特点。设计是分析的逆过程。

3.在分析和设计同步时序逻辑电路时,把CP信号作逻辑1处理,对异步时序逻辑电路则把CP 信号作为一个变量。

提醒:《由主从JK触发器组成的8421码异步五进制计数器》最后刷新时间 2023-07-10 03:57:09,本站为公益型个人网站,仅供个人学习和记录信息,不进行任何商业性质的盈利。如果内容、图片资源失效或内容涉及侵权,请反馈至,我们会及时处理。本站只保证内容的可读性,无法保证真实性,《由主从JK触发器组成的8421码异步五进制计数器》该内容的真实性请自行鉴别。