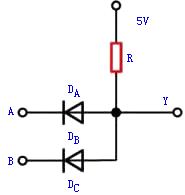

1、二极管与门电路

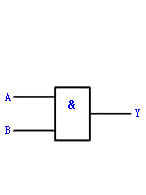

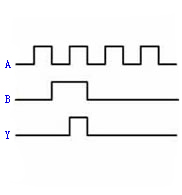

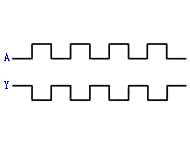

图1(a)所示是二极管与门电路,它有两个输入端A和B,一个输出端Y。也可以认为A和B是它的两个输入信号或称输入变量,Y是输出信号或称输出变量。图1(b)和(c)所示分别为与门电路的逻辑符号和波形图。

|

|

|

| (a)电路 | (b)逻辑符号 | (c)波形图 |

|

图1 二极管与门电路 | ||

当输入变量A和B全为1时(设两个输入端的电位均为3V),电源+5V的正端经电阻R向两个输入端流通电流(电源的负端接“地”,图中未标出), 和

和 两管都导通,输出端Y的电位略高于3V(因二极管的正向电压降有零点几伏),因此输出变量Y为1。

两管都导通,输出端Y的电位略高于3V(因二极管的正向电压降有零点几伏),因此输出变量Y为1。

当输入变量不全为1,而有一个或两个全为0时,即该输入端的电位在0V附近。例如A为0,B为1,则 优先导通。这时输入端Y的电位也在0V附近,因此Y为0。

优先导通。这时输入端Y的电位也在0V附近,因此Y为0。 因承受反向电压而截止。

因承受反向电压而截止。

只有当输入变量全为1时,输出变量Y才为1,这合乎与门的要求。与逻辑关系式为

(1)

(1)

图1(a)有两个输入端,输入信号有1和0两种状态,共有四种组合,因此可用表1完整地列出四种输入、输出逻辑状态。它可和图12.2(c)的波形图相对照。

|

表1 与门逻辑状态表 | ||

| A | B | Y |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

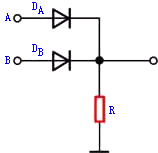

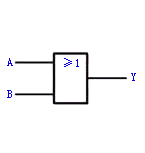

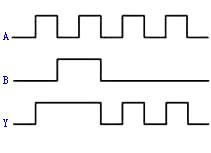

2、二极管或门电路

图2(a)所示是二极管或门电路。比较一下图1(a)和图2(a)就可看出,后者二极管的极性与前者接得相反,其阴极相连经电阻R接“地”。

|

|

|

| (a)电路 | (b)逻辑符号 | (c)波形图 |

| 图2 二极管或门电路 | ||

当输入变量只要有一个为1时,输出就为1。例如A为1,B为0,则 优先导通,输出变量Y也为1。

优先导通,输出变量Y也为1。 因承受反向电压而截止。

因承受反向电压而截止。

只有当输入变量全为0时,输出变量Y才为0,此时两只二极管都截止。或逻辑关系式为

(2)

(2)

表2是或门的输入、输出逻辑状态表,它可和图2(c)的波形图相对照。图2(b)是或门电路的逻辑符号。

|

表2 或门逻辑状态表 | ||

| A | B | Y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

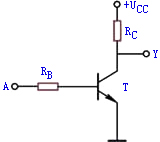

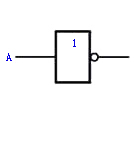

3、晶体管非门电路

图3(a)所示是晶体管非门电路。晶体管非门电路不同于放大电路,管子的工作状态或从截止转为饱和,或从饱和转为截止。非门电路只有一个输入端A。当A为1时,晶体管饱和,其集电极,即输出端Y为0(其电位在0V附近);当A为0时,晶体管截止,输出端Y为1(其电位近似等于 )。所以非门电路也称为反相器。非逻辑关系式为

)。所以非门电路也称为反相器。非逻辑关系式为

|

|

|

| (a)电路 | (b)逻辑符号 | (c)波形图 |

|

图3 晶体管非门电路 | ||

表3是非门逻辑状态表,它可和图3(c)的波形图相对照。图3(b)是非门电路的逻辑符号。

|

表3 非门逻辑状态表 | |

| A | Y |

| 0 | 1 |

| 1 | 0 |