译码和编码的过程相反。编码是将某种信号或十进制的10个数码(输入)编成二进制代码(输出)。译码是将二进制代码(输入)按其编码时的原意译成对应的信号或十进制数码(输出)。

1、二进制译码器

例如,要把输入的一组3位二进制代码译成对应的8个输出信号,其译码过程如下:

(1) 列出译码器的状态表

设输入3位二进制代码为ABC,输出8个信号低电平有效,设为 。每个输出代表输入的一种组合,并设ABC=000时,

。每个输出代表输入的一种组合,并设ABC=000时, ,其余输出为1;ABC=001时,

,其余输出为1;ABC=001时, ,其余输出为1;……;ABC=111时,

,其余输出为1;……;ABC=111时, ,其余输出为1,则列出的状态表见表1。

,其余输出为1,则列出的状态表见表1。

|

表1 74LS138型3位二进制译码器的状态表 | |||||||||||||

| 使能 | 控制 | 输入 | 输出 | ||||||||||

|

|

|

|

A |

B |

C |

|

|

|

|

|

|

|

|

|

0 |

× |

× |

|||||||||||

|

× |

1 |

× |

× |

× |

× |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

× |

× |

1 |

|||||||||||

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

×表示任意态

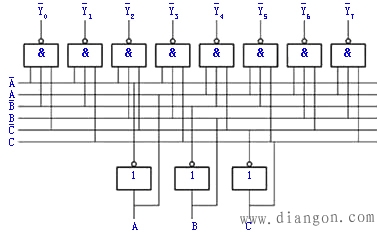

(2) 由状态表写出逻辑式

(3) 由逻辑式画出逻辑图(图1)

|

|

图1 3位二进制译码器 |

这种3位二进制译码器也称为3/8线译码器,最常用的是74LS138型译码器,表1就是它的功能表。它还有一个使能端 和两个控制端

和两个控制端 ,

, 。

。 高电平有效,

高电平有效, =1时,可以译码;

=1时,可以译码; 时禁止译码,输出全为1。

时禁止译码,输出全为1。 和

和 低电平有效,若均为0,可以译码;若其中有1或全1,则禁止译码,输出也全为1。

低电平有效,若均为0,可以译码;若其中有1或全1,则禁止译码,输出也全为1。

二进制译码器除3/8线译码器外,还有2/4线译码器和4/16线译码器。

2、二-十进制显示译码器

在数字仪表、计算机和其他数字系统中,常常要把测量数据和运算结果用十进制数显示出来。这就要用显示译码器,它能够把“8421”二-十进制代码译成能用显示器件显示出的十进制数。

常用的显示器件有半导体数码管、液晶数码管和荧光数码管等。下面只介绍半导体数码管一种。

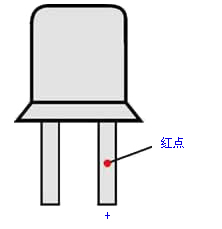

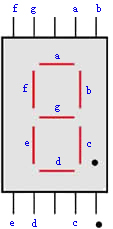

(1)半导体数码管

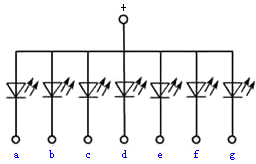

半导体数码管(或称LED数码管)的基本单元是发光二极管LED(英文Light Emitting Diode的缩写),它将十进制数码分成7个字段,每段为一发光二极管,其字形结构如图2(b)所示。选择不同的字段发光,可显示出不同的字形。例如,当ab,c,d,e,f,g7个字段全亮时,显示出8;b,c段亮时,显示出1。

|

|

| (a)发光二极管 | (b)字形结构 |

|

图2半导体数码管 | |

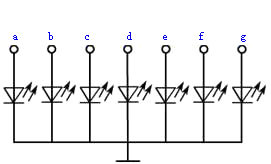

半导体数码管中7个发光二极管有共阴极和共阳极两种接法,如图3所示。前者,某一字段接高电平发光;后者,接低电平时发光。使用时每个管要串联限流电阻。

|

|

| (a)共阴极 | (b)共阳极 |

|

图3 半导体数码管两种接法 | |

(2)七段显示译码器

七段显示译码器的功能是把“8421”二-十进制代码译成对应于数码管的7个字段信号,驱动数码管,显示出相应的十进制数码。如果采用共阴极数码管,则输出状态应和表2所示的相反,即1和0对换。

|

表2 74LS247 型七段译码器的功能表 | |||||||||||||||

| 功能和十进制数 | 输入 | 输出 | 显示 | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| 试灯 |

0 |

× |

1 |

× |

× |

× |

× |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

8 |

| 灭灯 |

× |

× |

0 |

× |

× |

× |

× |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

全灭 |

| 灭0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

灭0 |

|

0 1 2 3 4 5 6 7 8 9 |

1 1 1 1 1 1 1 1 1 1 |

1 × × × × × × × × × |

1 1 1 1 1 1 1 1 1 1 |

0 0 0 0 0 0 0 0 1 1 |

0 0 0 0 1 1 1 1 0 0 |

0 0 1 1 0 0 1 1 0 0 |

0 1 0 1 0 1 0 1 0 1 |

0 1 0 0 1 0 0 0 0 0 |

0 0 0 0 0 1 1 0 0 0 |

0 0 1 0 0 0 0 0 0 0 |

0 1 0 0 1 0 0 1 0 0 |

0 1 0 1 1 1 0 1 0 1 |

0 1 1 1 0 0 0 1 0 0 |

1 1 0 0 0 0 0 1 0 0 |

0 1 2 3 4 5 6 7 8 9 |

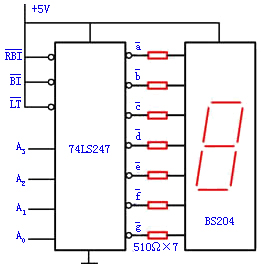

表2所例举的是74LS247型译码器的功能表,图3是它的外引线排列图。它有4个输入端 ,

, ,

, ,

, 和7个输出端

和7个输出端 (低电平有效),后者接数码管七段。此外,还有3个输入控制端,其功能如下:

(低电平有效),后者接数码管七段。此外,还有3个输入控制端,其功能如下:

(1) 试灯输入端 用来检验数码管的七段是否正常工作。当

用来检验数码管的七段是否正常工作。当 ,

, 时,无论

时,无论 ,

, ,

, ,

, 为何状态,输出

为何状态,输出 均为0,数码管七段全亮,显示“8”字。

均为0,数码管七段全亮,显示“8”字。

(2) 灭灯输入端 当

当 ,无论其他输入信号为何状态,输出

,无论其他输入信号为何状态,输出 均为1,数码管七段全灭,无显示。

均为1,数码管七段全灭,无显示。

(3) 灭0输入端 当

当 ,

, ,

, ,只有当

,只有当 时,输出

时,输出 均为1,不显示0字;这时,如果

均为1,不显示0字;这时,如果 ,则译码器正常输出,显示0。当

,则译码器正常输出,显示0。当 为其他组合时,不论

为其他组合时,不论 为0或1,译码器均可正常输出。此输入控制信号常用来消除无效0。例如,可消除000.001前两个0,则显示出0.001。

为0或1,译码器均可正常输出。此输入控制信号常用来消除无效0。例如,可消除000.001前两个0,则显示出0.001。

上述3个输入控制端均为低电平有效,在正常工作时这3个输入端均接高电平。

|

|

|

图5七段译码器和数码管的连接图 |

图4 74LS247型译码器的外引线排列图 |

图5所示是74LS247型译码器和共阳极BS204型半导体数码管的连接图。