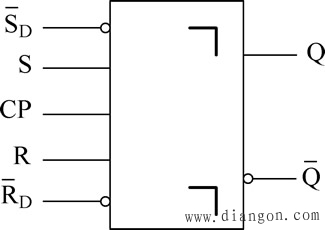

主从RS触发器的逻辑图形符号如图1所示。逻辑图形中的“┐”表示“延迟输出”,即CP返回0以后输出状态才改变。因此触发器状态的变化发生在CP的下降沿。

|

| 图1 主从RS触发器的图形符号 |

主从RS触发器的特性表如表1所示。

| 表1 主从RS触发器的特性表 |

| CP | S | R | Qn | Qn+1 |

| × | × | × | × | Qn |

| 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 1 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | × | |

| 1 | 1 | 1 | × |

从表1中可以看出,主从RS触发器只在时钟脉冲的下降沿触发,除此之外的任何时刻,不论输入端和触发器的原态如何,触发器始终保持原态。主从结构的RS触发器正常工作时,仍然要遵循约束条件:RS=0。