前面讲过的各种电路结构的触发器都是以RS触发器为例介绍的。可以发现,不论哪种结构的RS触发器,在使用时都要遵循RS=0的约束条件,这样就为工作带来了极大的不便,同时也降低了时序逻辑电路的抗干扰能力。因此,人们在RS触发器的基础上研究出了另一种类型的触发器——JK触发器。JK触发器完全取消了使用时的约束条件,不论输入端J和K的状态如何,都能唯一确定触发器的次态。下面以主从结构的JK触发器(简称主从JK触发器)为例,详细介绍JK触发器的电路结构和工作原理。

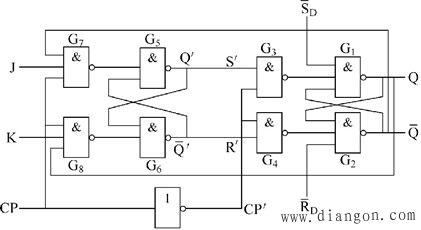

图1(a)所示为主从JK触发器的电路结构。从电路图中可以看到,主从JK触发器是在主从RS触发器的基础上,将输出Q和![]() 分别反馈到输入与非门G7和G8的输入上得到的。为了表示该电路与主从RS触发器逻辑功能的区别,将R和S分别用J和K代替。

分别反馈到输入与非门G7和G8的输入上得到的。为了表示该电路与主从RS触发器逻辑功能的区别,将R和S分别用J和K代替。

|

|

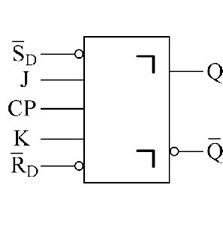

| 1(a) 电路结构 | 1(b) 逻辑符号 |

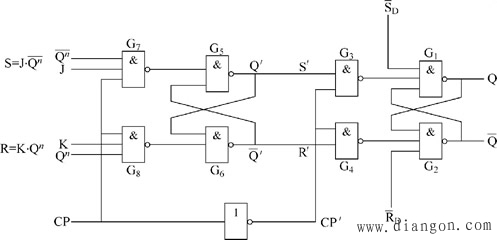

下面分析主从JK触发器的逻辑功能。为了分析的方便,把图1(a)所示的主从JK触发器的电路图变换成主从RS触发器的形式,如图2所示。

|

| 图2 等效成主从RS触发器的主从JK触发器 |

与主从RS触发器相同,当CP=0时,主从JK触发器保持原态;当CP=1期间,主从JK触发器仍然保持原态;只有当时钟脉冲CP的下降沿(从1跳转为0)来临时,主从JK触发器的状态(Q)才变为与主触发器的状态(![]() )一致,如图2所示。下面分析主从JK触发器输入端J、K与输出端(Q)之间的对应关系。

)一致,如图2所示。下面分析主从JK触发器输入端J、K与输出端(Q)之间的对应关系。

(1)J=K=0

若CP=1,Qn=0时,则![]() ,

,![]() ,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态不变。

,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态不变。

若CP=1,Qn=1时,则![]() ,

,![]() ,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态不变。

,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态不变。

故J=K=0时,当时钟脉冲CP的下降沿来临时,主从JK触发器状态不变。

(2)J=0,K=1

若CP=1,Qn=0时,则![]() ,

,![]() ,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态不变,即Qn+1=0。

,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态不变,即Qn+1=0。

若CP=1,Qn=1时,则![]() ,

,![]() ,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态变为0态,即Qn+1=0。

,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态变为0态,即Qn+1=0。

故J=0,K=1时,当时钟脉冲CP的下降沿来临时,主从JK触发器状态变为0态,即Qn+1=0。

(3)J=1,K=0

若CP=1,Qn=0时,则![]() ,

,![]() ,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态变为1态,即Qn+1=1。

,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态变为1态,即Qn+1=1。

若CP=1,Qn=1时,则![]() ,

,![]() ,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态不变,即Qn+1=1。

,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态不变,即Qn+1=1。

故J=1,K=0时,当时钟脉冲CP的下降沿来临时,主从JK触发器状态变为1态,即Qn+1=1。

(4)J=K=1

若CP=1,Qn=0时,则![]() ,

,![]() ,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态变为1态,即Qn+1=1。

,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态变为1态,即Qn+1=1。

若CP=1,Qn=1时,则![]() ,

,![]() ,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态变为0态,即Qn+1=0。

,根据主从RS触发器的特性表1可知,当时钟脉冲CP的下降沿来临时,触发器状态变为0态,即Qn+1=0。

故J=K=1时,当时钟脉冲CP的下降沿来临时,主从JK触发器状态翻转。原态为0,翻转后即为1;原态为1,翻转后即为0。

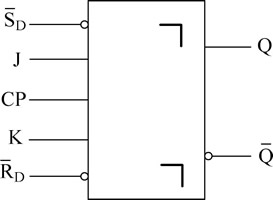

主从JK触发器特性表如表2所示。其逻辑图形符号如图2所示。

|

| 图2 主从JK触发器的逻辑符号 |

主从JK触发器的动作特点符合主从型触发器的动作特点。但从表2中可以看出,JK触发器解决了对触发器输入状态的限制,不论JK触发器的输入端是何种状态,触发器触发之后都有相应稳定的状态与之对应。但它仍然存在主从型触发器的缺点,即CP下降沿来临时从触发器的状态不一定能按此刻输入信号的状态来确定,而必须考虑整个CP=1期间里输入信号的变化情况,才能确定触发器的次态。边沿触发器很好地解决了这个问题。

| 表2 主从JK触发器的特性表 |

| CP | J | K | Qn | Qn+1 |

| × | × | × | × | Qn |

| 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 1 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 0 |