主从结构的触发器,解决了触发器在CP=1期间的空翻现象。但由于主触发器本身是同步RS触发器,因此在CP=1期间,主触发器的状态![]() 仍然会随着R和S状态的变化而多次改变。这样,会导致在CP下降沿来临时,触发器状态的变化与特性表不符。

仍然会随着R和S状态的变化而多次改变。这样,会导致在CP下降沿来临时,触发器状态的变化与特性表不符。

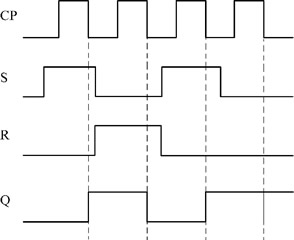

例1 图1所示的主从RS触发器电路中,已知CP、R和S的电压波形如图1所示试画出Q的电压波形。设触发器工作前已清零。

|

| 图1 例1电压波形图 |

解:因为主从结构的触发器的状态只在时钟脉冲下降沿到来时触发,因此沿时钟脉冲的下降沿画出虚线,在虚线处根据R和S的状态查主从触发器的特性表1,画出触发器翻转后的状态,其余时刻触发器保持原态。

主从RS触发器的输出电压波形如图1所示。

例1情况比较简单,即在CP=1期间,输入信号R和S的状态不发生改变,在这种情况下,只要根据时钟脉冲下降沿处R和S的状态确定触发器的状态即可。但如果在CP=1期间,输入信号R和S的状态发生了改变,就必须根据主触发器的状态![]() 确定从触发器的状态变化;否则,会出现错误。

确定从触发器的状态变化;否则,会出现错误。

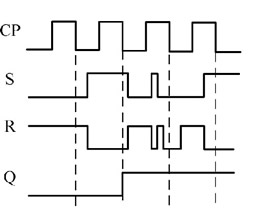

例2 图1所示的主从RS触发器电路中,已知CP、R和S的电压波形如图所示,试画出Q的电压波形。设触发器工作前已清零。

解:在本例中,存在着在CP=1期间,输入信号R和S的状态发生改变的情况,如果利用例1的方法,画出Q的电压波形如图2(a)所示。

|

|

| 2(a) 错误的输出波形 | 2(b) 正确的输出波形 |

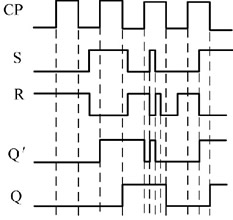

由图1可知,在CP=1期间,输入信号R和S的状态发生改变时,主触发器的状态![]() 随之发生变化,当时钟脉冲的下降沿来临时,从触发器翻转为主触发器的状态。

随之发生变化,当时钟脉冲的下降沿来临时,从触发器翻转为主触发器的状态。

因此在这种情况下,应该先画出主触发器的状态![]() 的波形,然后再根据

的波形,然后再根据![]() 画出Q的波形,如图2(b)所示。

画出Q的波形,如图2(b)所示。

可以看到,图2(a)和图2(b)中Q的波形不同,图2(b)是正确的。

因此,主从结构的触发器在CP=1期间输入信号发生变化时,CP下降沿来临时从触发器的状态不一定能按此刻输入信号的状态来确定,而必须考虑整个CP=1期间里输入信号的变化情况才能确定触发器的次态。这一特点大大降低了包含主从触发器的时序逻辑电路的抗干扰能力。

最理想的情况是,不论CP=1期间输入信号如何变化,CP下降沿来临时从触发器的状态都能按此刻输入信号的状态来确定。这样就产生了另一种结构的触发器——边沿触发器。