计数器使用以统计输入脉冲CP个数的时序逻辑电路,在数字系统中得到了最广泛的使用。

计数器的种类很多。按计数器中各触发器翻转是否与计数脉冲同步,可以分为同步计数器和异步计数器;按照计数器的技术过程中数字的增减,又可以分为加法计数器、减法计数器和加/减计数器。按计数进制可分为二进制计数器和非二进制计数器。非二进制计数器中最典型的是十进制计数器。下面主要以同步计数器为例进行介绍。

能够实现二进制计数功能的计数器称为二进制计数器。二进制计数器有加法计数器、减法计数器和加/减计数器,同时也有同步和异步之分。

一位二进制计数器只包含一个触发器,只能计数2个状态,两位二进制计数器包含两个触发器,能计数4个状态,3位二进制计数器包含3个触发器,能计数8个状态,以此类推,n位二进制计数器包含n个触发器,能计数2n个状态。4位二进制计数器是数字系统中最常用的逻辑器件,因为它的最大计数为16,因此4位二进制计数器又称为十六进制计数器。

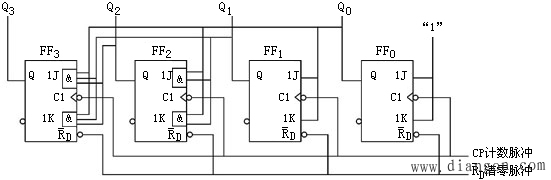

图1所示为由4个JK触发器构成的同步二进制加法计数器电路。图中各触发器的时钟脉冲输入端接同一计数脉冲CP,显然,这是一个同步时序电路。下面就用前面讲过的同步时序逻辑电路分析方法分析一下这个电路的逻辑功能。

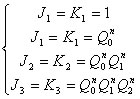

1、列出各出发器的驱动方程

|

(1) |

|

| 图1 4位同步二进制加法计数器 |

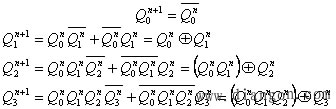

2、写出各触发器的状态方程

将个触发器的驱动方程带入![]() ,得到个触发器的状态方程:

,得到个触发器的状态方程:

|

(2) |

3、根据状态方程列出状态转换表

状态转换表见1

| 表1 74LS175的功能表 |

| 计数脉冲序号 | 电路状态 | 等效十进制属 | |||

| Q3 | Q2 | Q1 | Q4 | ||

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 |

| 2 | 0 | 0 | 1 | 0 | 2 |

| 3 | 0 | 0 | 1 | 1 | 3 |

| 4 | 0 | 1 | 0 | 0 | 4 |

| 5 | 0 | 1 | 0 | 1 | 5 |

| 6 | 0 | 1 | 1 | 0 | 6 |

| 7 | 0 | 1 | 1 | 1 | 7 |

| 8 | 1 | 0 | 0 | 0 | 8 |

| 9 | 1 | 0 | 0 | 1 | 9 |

| 10 | 1 | 0 | 1 | 0 | 10 |

| 11 | 1 | 0 | 1 | 1 | 11 |

| 12 | 1 | 1 | 0 | 0 | 12 |

| 13 | 1 | 1 | 0 | 1 | 13 |

| 14 | 1 | 1 | 1 | 0 | 14 |

| 15 | 1 | 1 | 1 | 1 | 15 |

| 16 | 0 | 0 | 0 | 0 | 0 |

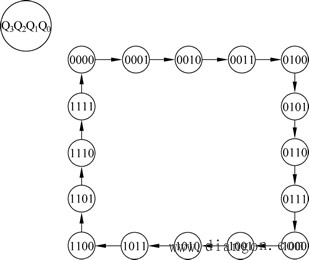

4、画出状态转移图和时序图

4位同步二进制计数器的状态转移图如图2所示。

|

| 图2 4位同步二进制计数器的状态转移图 |

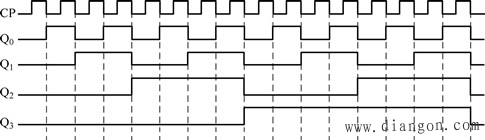

图3所示为4位同步二进制计数器电路的时序图。

|

| 图3 4位同步二进制计数器的时序图 |

由图3可以看出,输出端Q0、Q1、Q2、Q3输出脉冲的频率分别是时钟脉冲CP信号频率的1/2、1/3、1/4、1/8、1/16。因此如果将CP当做输入的基准信号,可以通过输出端Q0、Q1、Q2、Q3对CP信号进行分频。因此,计数器除了具有计数功能以外,还具有分频的功能。在数字电路中,还可以将计数器当作分频器使用。

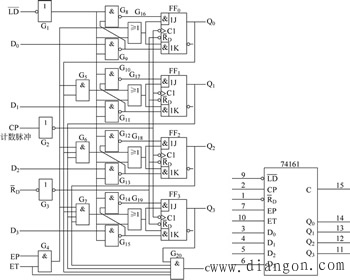

图4所示为集成的4位同步二进制计数器74161的逻辑图和图形符号。

|

| 图4 集成4位同步二进制计数器74161的逻辑图及图形符号 |

这个电路除了具有二进制加法计数功能以外,还具有预置数、保持和异步置零等附加功能。图中![]() 为预置数控制端,D0~D3为数据输入端,C为进位输出端,

为预置数控制端,D0~D3为数据输入端,C为进位输出端,![]() 为异步清零端(复位端),EP、ET为工作状态控制端。表2所示为74161的逻辑功能表。

为异步清零端(复位端),EP、ET为工作状态控制端。表2所示为74161的逻辑功能表。

| 表2 74161的逻辑功能表 |

| 清零 | 预置 | 使能 | 时钟 | 预置数据输入 | 输出 | 工作模式 | |||||||

| EP | ET | CP | D3 | D2 | D1 | D4 | Q3 | Q2 | Q1 | Q4 | |||

| 0 | × | × | × | × | × | × | × | × | 0 | 0 | 0 | 0 | 异步清零 |

| 1 | 0 | × | × | ↑ | d3 | d2 | d1 | d4 | d3 | d2 | d1 | d4 | 同步置数 |

| 1 | 1 | 0 | × | × | × | × | × | × | 保持 | 数据保持 | |||

| 1 | 1 | × | 0 | × | × | × | × | × | 保持 | 数据保持(C—0) | |||

| 1 | 1 | 1 | 1 | ↑ | × | × | × | × | 计数 | 加法计数 | |||

由表2可知,74161具有以下功能:

(1)异步清零。当![]() =0时,不管其他输入端的状态如何,不论有无始终脉冲CP,计数器输出端将被直接置零(Q3Q2Q1Q0=0000),称为异步清零。

=0时,不管其他输入端的状态如何,不论有无始终脉冲CP,计数器输出端将被直接置零(Q3Q2Q1Q0=0000),称为异步清零。

(2)同步并行预置数。当![]() =1,

=1,![]() =0时,在输入时钟CP上升沿的作用下,并行输入端的数据D3D2D1D0被置入计数器的输出端,即输入端的数据Q3Q2Q1Q0=D3D2D1D0。由于这个操作要与CP上升沿同步,所以称为同步预置数。

=0时,在输入时钟CP上升沿的作用下,并行输入端的数据D3D2D1D0被置入计数器的输出端,即输入端的数据Q3Q2Q1Q0=D3D2D1D0。由于这个操作要与CP上升沿同步,所以称为同步预置数。

(3)计数。当![]() =1,

=1,![]() =1,EP=ET=1时,在CP端输入计数脉冲,计数器进行二进制加法计数。

=1,EP=ET=1时,在CP端输入计数脉冲,计数器进行二进制加法计数。

(4)保持。当![]() =1,

=1,![]() =1,EP·ET=0时,即两个使能端中有0时,则计数器保持原来的状态不变。这时,如EP=0,则进位输出信号C保持不变;如ET=0,则进位输出信号C=0。

=1,EP·ET=0时,即两个使能端中有0时,则计数器保持原来的状态不变。这时,如EP=0,则进位输出信号C保持不变;如ET=0,则进位输出信号C=0。