根据计数器的计数容量,把能够进行N进制计数功能的计数器称为任意进制的计数器。从降低成本的角度考虑,厂家不可能生产任意进制的计数器,只可能生产某些常用的、批量较大的集成计数器芯片,如十进制计数器、十六进制计数器等。其他进制的计数器可以利用现有的集成计数器芯片通过适当的连接来实现。

设已有的计数器是N进制计数器,要设计的计数器是M进制计数器。下面分N>M和N<M两种情况来讨论任意进制。

可以采用置零法和置数法来设计任意进制的计数器。以具体的例子来介绍任意进制计数器的设计方法。

例1 利用同步十进制计数器74160设计同步六进制计数器。

解:由同步十进制计数器74160的功能表可知,74160有异步置零和同步置数的功能。所以,对于74160计数器,既可以采用异步置零的方法设计,也可以采用同步置数的方法设计。

|

1、置零法 |

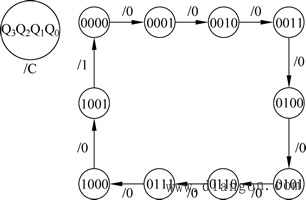

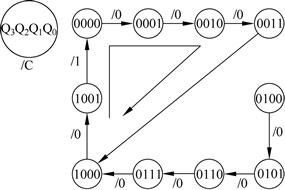

画出同步十进制计数器74160有效状态转移图如图1所示。

|

| 图1 74160的有效状态转移图 |

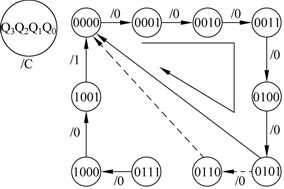

当计数器从状态0000(S0)开始计数,接收了6(M)个计数脉冲后,计数器状态为0110(SM)。如果将SM状态译码成一个清零信号加到计数器的异步清零端RD(RD=0),计数器将立刻清零,回到0000(SO)状态。由此可见,计数器从状态0110变为0000不需要计数脉冲的作用,计数器的状态0110(SM)只是一个瞬间即失的状态,从宏观表现上看,计数器好像从状态0101(SM-1)直接跳转到0000(SO)状态,状态0000~1010为所设计计数器的有效状态,共有6个,即六进制计数器,如图2(a)所示。

|

|

| 图2(a) 异步置零法 | 图2(b) 同步置零法 |

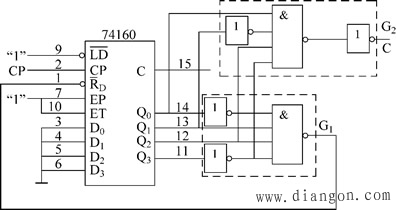

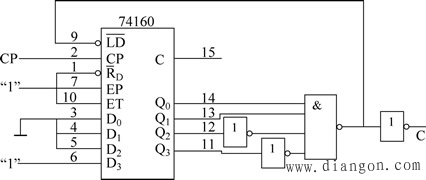

采用异步置零法利用同步十进制计数器74160设计六进制计数器的电路,如图3所示。

|

| 图3 将十进制计数器74160转换成六进制计数器的电路 |

由图3可知,由于74160为异步清零功能,即清零端输入清零信号后,不需要计数脉冲的作用即可清零,因此由状态0110(SM)译出清零信号加到清零端RD译码器电路为G1门电路。计数器都有进位输出,通常由计数器的最后一个有效状态译成进位输入信号。因此,由状态0101(SM-1)译出进位输出信号C。译码器为门电路G2。

由前面的分析可知,在计数脉冲的作用下,计数器状态从全零状态SO开始变为某个状态后,在清零信号的作用下,使计数脉冲清零,又回到全零状态SO,完成一个计数循环,得到任意进制计数器。这种设计任意计数器的方法称为置零法,它适用于有置零输入端的计数器。

因为计数器的清零功能分为异步清零和同步清零,因此置零法又分为同步置零法和异步置零法。他们的区别在于计数器清零是否需要计数脉冲的作用:需要计数脉冲作用的清零称为同步清零,不需要计数脉冲作用的清零称为异步清零。

异步清零法和同步清零法也略有不同。有同步清零功能的,需要从SM-1状态译出清零信号,当下一个计数脉冲到达时,计数器才清零,回到全零状态SO,如图2(b)所示。

|

2、置数法 |

由于74160有同步置数的功能,因此也可采用同步置数的方法设计六进制计数器。

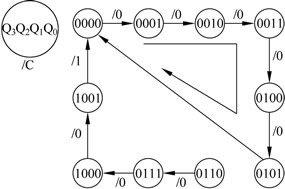

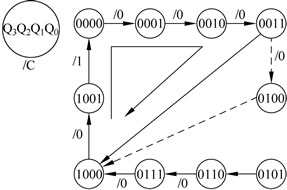

设预置数输入端D3D2D1D0=1000,则当同步预置数控制端LD=0,且下一个计数脉冲到来时,计数器输入端的状态变为预置数输入端的状态Q3Q2Q1Q0=1000。因此,为了得到六进制计数器,从十进制的有效状态1000开始,沿着有效状态循环的方向数5(M-1)个计数脉冲到状态0011,由该状态译出一个同步预置数信号端LD,即得到了所设计的六进制计数器。状态1000~0011为六进制计数器的有效状态,六进制计数器的进位输出由其中一个有效状态译出即可,如图4(a)所示。

|

|

| 图4(a) 异步置零法 | 图4(b) 同步置零法 |

采用同步置数法利用同步十进制计数器74160设计六进制计数器的电路如图5所示。

|

| 图5 采用同步置数法设计六进制计数器的电路图 |

同步置数法适用于同步预置数功能的计数器。对于有异步置数功能的计数器只能采用异步置数的方法设计任意进制计数器。异步置数法与同步置数法也略有不同,对于异步置数功能的计数器,只要异步置数控制端LD=0信号一出现,不用计数脉冲CP控制,计数器立即开始将预置数输入端的状态置入输出端。如图4(b)所示,若设计M进制的计数器,则从预置数状态开始,计数M个计数脉冲后所对应的状态译出异步预置数信号输入到LD。