来源:本站

导读:目前正在解读《NMOS逻辑门电路》的相关信息,《NMOS逻辑门电路》是由用户自行发布的知识型内容!下面请观看由(

电工学习网 - www.9pbb.com)用户发布《NMOS逻辑门电路》的详细说明。

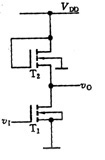

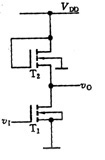

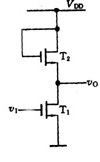

NMOS逻辑门电路是全部由N沟道MOSFET构成。由于各种器件具有较小的几何尺寸,适合于制造大规模集成电路。此外,由于NMOS集成电路的结构简单,易于使用CAD技术进行设计。与CMOS电路相似,NMOS电路中不使用难于制造的电阻。NMOS反相器是整个NMOS逻辑门电路的基本构件,它的工作管常用增强型器件,而负载管可以是增强型也可以是耗尽型。现以增强型器件作为负载管的NMOS反相器为例来说明它的工作原理。

|

|

| (a)实际电路 |

(b)简化画法 |

| 1 NMOS反相器 |

图1(a)表示NMOS反相器的原理电路,其中T1为工作管,T2为负载管,二者均属增强型器件。若T1和T2在同一工艺过程中制成,它们必将具有相同的开启电压VT。图1(b)是它的简化画法。由图1可见,负载管T2的栅极与漏极同接电源VDD,因而T2总是工作在它的恒流区,处于导通状态。

当输入vI为高电压(超过管子的开启电压VT)时,T1导通,输出vO为低电压。输出低电压的值由T1、T2两管导通时所呈现的电阻值之比决定。通常T1的跨导gm1远大于T2管的跨导gm2,以保证输出低电压值在+1V左右。当输入电压vI为低电压(低于管子的开启电压VT)时,T1截止,输出vO为高电压。由于T2管总是处于导通状态,因此输出高电压值约为(VDD-VT)。通常gm1在100~200μS之间,而gm2约为5~15μS。T1导通时的等效电阻Rds1约为3~10kΩ,而T2的Rds2约在100~200kΩ之间。负载管导通电阻是随工作电流而变化的非线性电阻。

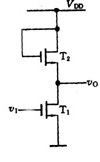

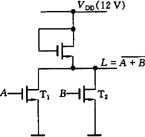

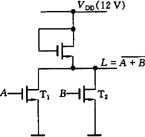

在NMOS反相器的基础上,可以制成NMOS门电路。图2为NMOS或非门电路。

|

图2 MNOS或非门电路 |

只要输入A、B中任一个为高电平,与它对应的MOSFET导通时,输出为低电平;仅当A、B全为低电平,所有工作管都截止时,输出才为高电平。可见电路具有或非功能,即

或非门的工作管都是并联的,增加管子的个数,输出低电平基本稳定,在整体电路设计中较为方便,因而NMOS门电路是以或非门为基础的。这种门电路主要用于大规模集成电路。

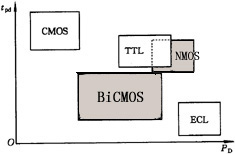

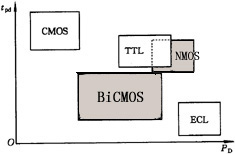

以上讨论和分析了各种逻辑门电路的结构、工作原理和性能,以便于比较,现用它们的主要技术参数传输延迟时间tpd和功耗PD综合描述各种逻辑门电路的性能,如图3所示。

|

图3 各种门电路的延迟时间与功耗的关系图 |

提醒:《NMOS逻辑门电路》最后刷新时间 2023-07-10 03:58:10,本站为公益型个人网站,仅供个人学习和记录信息,不进行任何商业性质的盈利。如果内容、图片资源失效或内容涉及侵权,请反馈至,我们会及时处理。本站只保证内容的可读性,无法保证真实性,《NMOS逻辑门电路》该内容的真实性请自行鉴别。