计数器能累计输入脉冲的数目,可以进行加法、减法或两者兼有的计数,可分为二进制计数器、十进制计数器及任意进制计数器。

表1是4位二进制加法计数器的状态表,要实现4位二进制加法计数,必须用4个双稳态触发器,他们具有计数功能,下面介绍两种二进制加法计数器。

表1 4位二进制加法计数器的状态表

| 计数脉冲数 | 二进制数 | 十进制数 | |||

|

|

|

| ||

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 |

| 2 | 0 | 0 | 1 | 0 | 2 |

| 3 | 0 | 0 | 1 | 1 | 3 |

| 5 | 0 | 1 | 0 | 1 | 5 |

| 6 | 0 | 1 | 1 | 0 | 6 |

| 7 | 0 | 1 | 1 | 1 | 7 |

| 8 | 1 | 0 | 0 | 0 | 8 |

| 9 | 1 | 0 | 0 | 1 | 9 |

| 10 | 1 | 0 | 1 | 0 | 10 |

| 11 | 1 | 0 | 1 | 1 | 11 |

| 12 | 1 | 1 | 0 | 0 | 12 |

| 13 | 1 | 1 | 0 | 1 | 13 |

| 14 | 1 | 1 | 1 | 0 | 14 |

| 15 | 1 | 1 | 1 | 1 | 15 |

| 16 | 0 | 0 | 0 | 0 | 16 |

1、异步二进制加法计数器

由表1可见:

(1) 每来一个计数脉冲,最低位触发器翻转一次;

|

| 图1 由主从型JK触发器组成的异步4位二进制加法计数器 |

(2) 高位触发器是在相邻的低位触发器从1变为0进位时翻转。

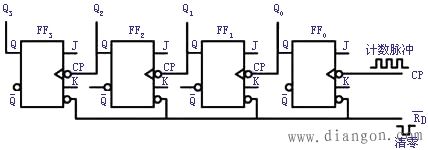

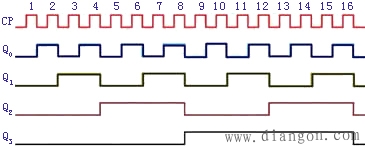

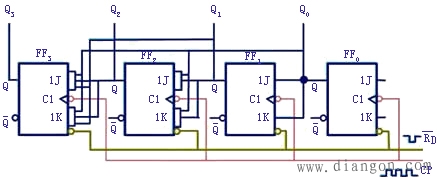

因此,可用4个主从型JK触发器来组成异步4位二进制加法计数器,如图2所示,每个触发器的J、K端悬空,相当于1,故具有计数功能。触发器的进位脉冲从Q端输出送到相邻高位触发器的CP端,这符合主从型触发器在下降沿触发的特点。图2是它的工作波形图。

|

| 图2 图1所示二进制加法计数器的工作波形图 |

这种所以称为“异步”加法计数器,是由于计数脉冲不是同时加到各位触发器,而只加到最低位触发器,其他各位触发器则由相邻低位触发器输出的进位脉冲来触发,因此他们的状态的变换有先有后,是异步。

2、同步二进制加法计数器

如果计数器还是用4个主从型JK触发器组成,根据表1可得出各位触发器的J,K端的逻辑关系式:

(1)第一位触发器 ,每来一个计数脉冲就翻转一次,故

,每来一个计数脉冲就翻转一次,故 ;

;

(2)第二位触发器 ,在

,在 时再来一个脉冲才翻转,故

时再来一个脉冲才翻转,故 ;

;

(3)第三位触发器 ,在

,在 时再来一个脉冲才翻转,故

时再来一个脉冲才翻转,故 。

。

(4)第四位触发器 ,在

,在 时再来一个脉冲才翻转,故

时再来一个脉冲才翻转,故 。

。

因此,可得出图3所示的同步4位二进制加法计数器。由于计数脉冲同时加到各位触发器,它们的状态变换与计数脉冲同步,这是“同步”名称的由来。显然,同步计数器的计数速度教异步为快。

|

| 图3 由主从型JK触发器组成的同步4位二进制加法计数器 |

图中,触发器 和

和 有多个J端和K端,J端之间和K端之间都是与的逻辑关系。

有多个J端和K端,J端之间和K端之间都是与的逻辑关系。

在上述的4位二进制加法计数器中,当输入第十六个计数脉冲时,又将返回起始状态0000。如果还有第5位触发器的话,这时应是10000,即十进制数16。但是现在只有4位,这个数就记录不下来,这称为计数器的溢出。因此,4位二进制加法计数器,能记的最大十进制数为 。n位二进制加法计数器,能记的最大十进制数为

。n位二进制加法计数器,能记的最大十进制数为 。

。