触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存贮器件,是构成各种时序电路的最基本逻辑单

| 元。 |

凡是在时钟信号作用下逻辑功能符合表1所示特性表所规定的逻辑功能者,就叫做RS触发器。

| 表1 RS特性表 |

| S | R | Qn+1 |

| 0 | 0 | Qn |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 不定 |

式(1)称为触发器的特性方程。

| (1) |

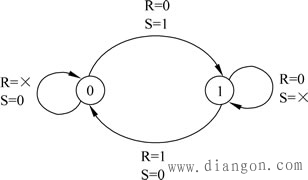

根据表5-1还可以用图形形象地表示出触发器状态转换的情况,如图1所示。

图中圆圈表示触发器的状态,箭头表示触发器状态转换的方向,箭头旁边注明的是状态转换的输入条件。这是表示触发器逻辑功能的另一种表示方法,称为状态转换图。状态转换图表示触发器从一个状态变化到另一个状态或保持原状态不变时,对输入信号的要求。

因此,描述触发器逻辑功能可以用上述3种方法:特性表、特性方程和状态转换图。这3种表示方法之间可以互相转换。

|

| 图1 RS触发器的状态转换图 |

![]() JK触发器

JK触发器

凡是在时钟信号作用下逻辑功能符合表2 所示特性表所规定的逻辑功能者,就叫做JK触发器。

| 表2 JK触发器特性表 |

| S | R | Qn+1 |

| 0 | 0 | Qn |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 翻转 |

同样,可以根据表2所示写出JK触发器的特性方程,经化简后得到

| (2) |

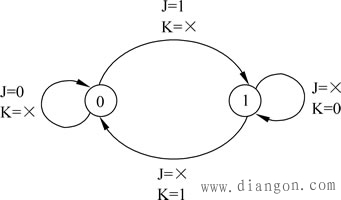

由表2可以画出JK触发器的状态转换图如图2所示。

|

| 图2 JK触发器的状态转换图 |

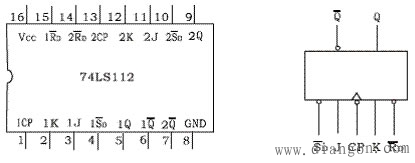

在输入信号为双端的情况下,JK触发器是功能完善、使用灵活和通用性较强的一种触发器。本实验采用74LS112 双JK触发器,是下降边沿触发的边沿触发器。引脚功能及逻辑符号如图3 所示。

|

| 图3 74LS112双JK触发器引脚排列及逻辑符号 |

| 表3 74LS112的功能表 |

| 输入 | 输出 | |||||

| CP | J | K | Qn+1 | |||

| 0 | 1 | × | × | × | 1 | 0 |

| 1 | 0 | × | × | × | 0 | 1 |

| 0 | 0 | × | × | × | φ | φ |

| 1 | 1 | ↓ | 0 | 0 | Qn | |

| 1 | 1 | ↓ | 1 | 0 | 1 | 0 |

| 1 | 1 | ↓ | 0 | 1 | 0 | 1 |

| 1 | 1 | ↓ | 1 | 1 | Qn | |

| 1 | 1 | ↑ | × | × | Qn | |

<—任意态 ↓—高到低电平跳变 ↑—低到高电平跳变

Qn(![]() )—现态 Qn+1(

)—现态 Qn+1(![]() )—次态 φ—不定态

)—次态 φ—不定态

K触发器常被用作缓存储器,移位寄存器和计数起器。

![]() D触发器

D触发器

凡是在时钟信号作用下逻辑功能符合表4所示特性表所规定的逻辑功能者,就叫做D触发器。

| 表4 D触发器特性表 |

| D | Qn+1 |

| 0 | 0 |

| 1 | 1 |

D触发器的特性方程为

| (3) |

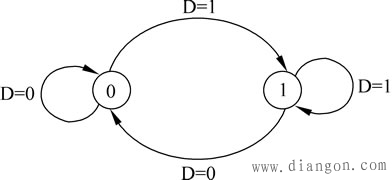

D触发器的状态转换图如图4所示。

|

| 图4 D触发器的状态转换图 |

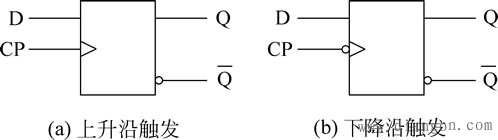

从表4可知,D触发器只有一个输入端D,其结构形式也有多种,图5所示为边沿型D触发器的逻辑图形符号,图5(a)所示为上升沿触发,图5(b)所示为下降沿触发。

|

| 图5 边沿型D触发器的图形符号 |

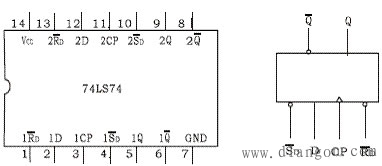

图6 为双D 74LS74 的引脚排列及逻辑符号。功能如表5。

|

| 图6 74LS74引脚排列及逻辑符号 |

| 表5 74LS112的功能表 |

| 输入 | 输出 | ||||

| CP | D | Qn+1 | |||

| 0 | 1 | × | × | 1 | 0 |

| 1 | 0 | × | × | 0 | 1 |

| 0 | 0 | × | × | φ | φ |

| 1 | 1 | ↑ | 1 | 1 | 0 |

| 1 | 1 | ↑ | 0 | 0 | 1 |

| 1 | 1 | ↓ | × | Qn | |