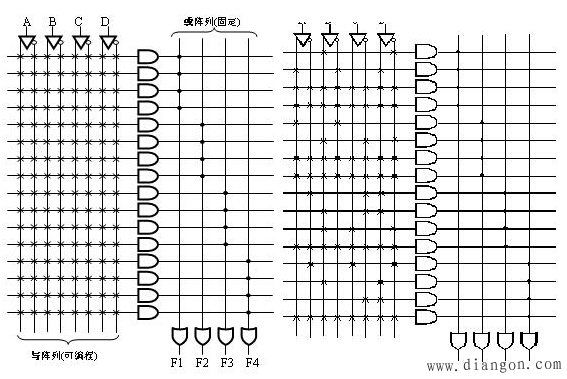

图1 PAL的电路结构 图2 编程后的PAL电路

一个16×4(16与门×4或门)PAL的基本结构如图1所示。它是由可编程的与门阵列和固定连接的或门阵列,以及其它附加的输出电路组成。与阵列的可编程使器件具有很多输入端,而固定的或阵列又使器件体积小、速度快。在尚未编程前,与逻辑阵列所有的交叉点均有快速熔丝连通。编程时将有用的熔丝保留,无用的熔丝熔断,就得到所需的电路。它实现了四种不同功能的逻辑函数。

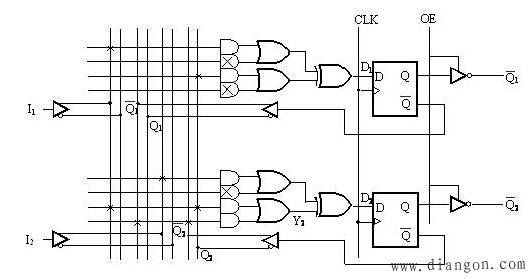

图2所示电路PAL器件内部只有与阵列和或阵列,这类器件适合构成组合逻辑电路。除此以外,PAL的输出单元有多种结构类型,如带反馈的阵列型、带反馈的寄存器型和异或型多种形式的输出、反馈电路结构。其中PAL的寄存器输出结构如图3所示。它在输出三态缓冲器和与或逻辑阵列输出之间串入了由D触发器组成的寄存器,并将触发器输出状态反馈到与逻辑阵列的输入端,该反馈功能使PAL电路具有记忆功能,并能方便地组成各种时序逻辑电路。该电路在D触发器和与和或逻辑阵列之间还可增设异或门,不仅可实现对数据的保持操作,而且可对与-或逻辑阵列输出的函数求反。在图3所示的编程情况下,当I1=0时,D1=Q2,当I1=1时D1=Q2,Q2在时钟信号CLK到来后翻转,即Q2n+1=Q2n 。而对下一个触发器,当I2=0时,D2=Q2I1+Q1Q2;当I2=1时,D2=Y2=Q2I1+Q1Q2,即得Y2的反函数。

PAL有多种结构类型,用户可根据使用需要,选择其阵列结构大小、输入输出的方式,以实现所需的各种逻辑功能。

图3 PAL的带异或门的寄存器输出结构