GAL按可编程结构可分为两大类:第一类阵列结构与PAL完全兼容,即与阵列可编程,或阵列固定,并且又增加了独特的“输出逻辑宏单元”结构,这类器件如GAL16V8、GAL20V8。第二类是与阵列和或阵列均可编程,这类器件也具有输出逻辑宏单元结构,如GAL39V8。但由于GAL39V8费用高,故使用较多的是GAL16V8、GAL20V8。

1. GAL的基本结构

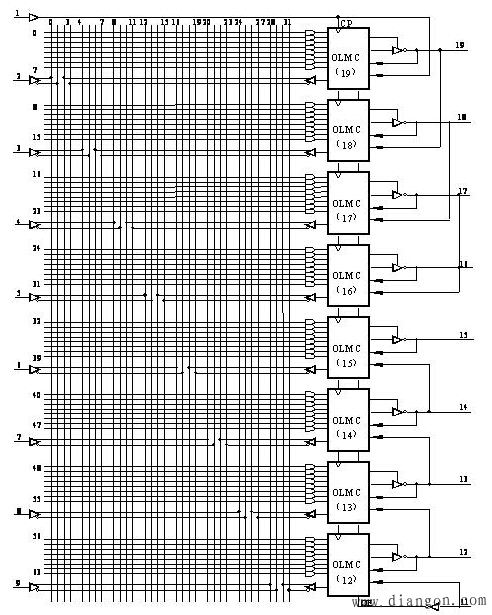

以常见的GAL16V8为例,介绍GAL器件的结构形式和工作原理。图1为GAL16V8的逻辑电路图。它由一个32×64位的可编程与逻辑阵列,8个OLMC,10个输入缓冲器、8个三态输出缓冲器和8个反馈/输入缓冲器等电路组成。

GAL16V8的每个输入正负信号和对应的反馈正负信号四列构成一个组,共8行输入32列。对每个OLMC有8个与门输入,共计64项。通过这样一个矩阵就可以把任何一个输入信号连同它的极性连接到要输出的任何一个与门上。与逻辑阵列的每个交叉点设有E2CMOS编程单元,其可编程的与阵列总码点数为2048个E2CMOS单元(64个乘积项和每个乘积项为32个输入端组成),对GAL的编程就是对这个与阵列的E2CMOS编程单元进行数据写入,实现相关点的编程连接,得到所需的逻辑函数。

图1 GAL16V8的逻辑结构图

在GAL16V8中 ,引脚 2—9作固定输入,引脚15、16作固定输出。而引脚12、13、14、17、18、19由三态门控制,即可以做输入端又可以作输出端。第1脚是专门用于CK的时钟输入端,第11脚是三态选通信号端OE,在组合电路中这两个引脚都可作为信号输入端。因此 ,这类芯片最多有16个输入脚 ,输出脚最多有8个,这也正是芯片型号中两个数字的含义。

GAL器件没有独立的或阵列结构,而是将各个或门放在各自输出逻辑宏单元OLMC中。

2. 输出逻辑宏单元(OLMC)

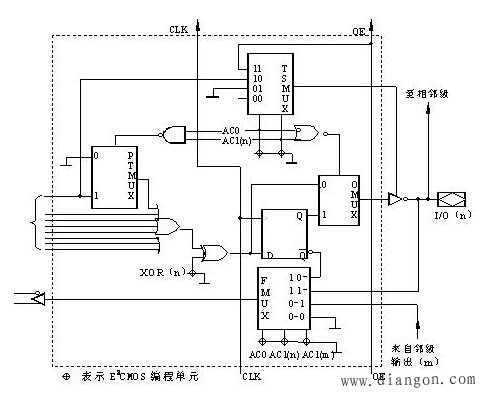

输出逻辑宏单元的结构如图2所示。它由一个或门、-个D触发器和4个数据选择器及-些门电路组成的控制电路。

OLMC的前级来自与阵列输出。在或门的输出端能产生不超过8项的与-或逻辑函数。图中的异或门用于控制输出信号的极性,XOR(n) 对应于结构控制字中的-位,n为各个OLMC的输出引脚号。当XOR(n)端为“1”时,异或门起反相器的作用,使输出信号高电平有效。否则XOR(n)端为“0”时,使输出信号低电平有效。D触发器对异或门输出状态作记忆作用,使GAL适用于时序逻辑电路。

每个OLMC有4个多路选择器:与与阵相连的积项多路选择开关PTMUX在ACn和ACl(n)控制下选择输入积项或“地”作为或门的输入。TSMUX用是选择输出三态缓冲器的选通信号开关,它由AG和ACi(n)控制,从VCC、OE、地和积项输入中选择允许输出的控制信号。FMUX决定反馈信号的来源,由AC0、AC1(n)和AC1(m)控制,其中n为对应的OLMC的输出引脚,而m代表与n相邻一位,即n+1和n-1。当FMUX输入端为“00”时,即把零电平反馈到与阵。当输入为“01”时,把邻单元输出作为输入反馈到与阵。当输入端为“10”时,把D触发器的输出Q反馈到与阵。当输入端为“ll”时,把宏单元输出反馈到与阵。OMUX则用于选择输出信号是组合的还是寄存的,它由AC0和AC1(n)选择OLMC输出是组合还是寄存器状态。当异或输出为“0”时是组合输出,异或输出为“l”时是寄存器输出。

图2 OLMC 的结构框图

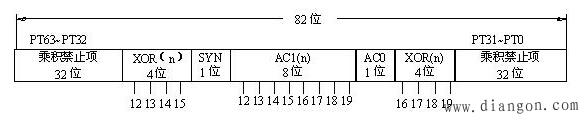

3. GAL的结构控制字

我们知道,这些多路选择器的不同输出得到不同的工作状态,而多路选择器的输出又取决于结构控制字AC0,AC1(n)、XOR(n)和SYN。GAL16V8的结构控制字如图所示。结构控制字共82位,XOR(n)和AC1(n), AC1(m)每路输出一位, AC0只有一个,为各路所公有。AC0、AC1(n) 和AC1(m)均为结构控制位,决定4个多路选择器输出的状态。SYN为同步位,它决定GAL是纯粹组合型输出(当SYN=1时),还是具有寄存器型输出能力(当SYN=0时)。结构控制字中还有64位乘积项禁止位,分别控制64个乘积项(PT0~PT63)屏蔽某些不用的乘积项。

GAL结构控制字决定了的GAL的各种编程工作模式。不同的结构控制字对应相应的编工作模式。

图3 GAL16V8的结构控制字

GAL的开发需要特定的开发软件和硬件编程器。一般情况下,首先在GAL的开发软件中,使用者应用某种编程语言编制描述其逻辑功能的程序,然后由开发软件的语言编译器对源文件进行编译,产生装入编程器的标准格式的JEDEC文件和设计文档文件。最后使用专用编程器写入GAL芯片,对结构控制字进行自动配置,就可以实现特定的逻辑功能。