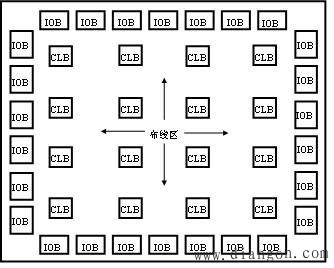

FPGA的生产厂家,以及产品种类较多,但它们的基本组成大致相似。FPGA的基本结构如图1所示。它的核心部分是逻辑单元阵列LCA,LCA是由内部逻辑块矩阵和周围I/O接口模块组成。LCA内部连线在逻辑块的行列之间,占据逻辑块I/O接口模块之间的通道,可以由可编程开关以任意方式连接形成逻辑单元之间的互连。

图1 FPGA的结构示意图

它由三种编程单元和一个存放编程数据的静态存储器组成。这三种可编程单元是由布线资源分隔的可编程逻辑模块CLB、周边可编程输入/输出单元IOB、布线通道中互连资源组成。CLB阵列实现用户指定的逻辑功能,它们以阵列的形式分布在FPGA中;可编程输入/输出单元 IOB为内部逻辑与器件封装引脚之间提供了可编程接口,它通常排列在芯片四周;可编程互连资源分布在CLB的空隙,互连资源可编程在模块之间传递的信号网络,用于实现各个CLB之间、CLB与IOB之间、以及全局信号与CLB与IOB之间的连接。FPGA利用户编程的查找表实现模块逻辑;程序控制多路复用器实现其功能选择。

FPGA的功能配置在于编程数据存贮器SRAM存放的编程数据决定,这些编程数据决定和控制各个CLB、IOB及内部连线的逻辑功能和它们之间的互连关系。静态存贮器SRAM的存贮单元是由两个CMOS反相器和-个用于读写数据的开关晶体管组成。两个CMOS反相器接成一个环路形成双稳态器件。这个器件的状态可以由字线选通位线上的外部信号传过器件重写。由于采用了独特的工艺设计,这种结构具有很强的抗干扰能力和很高的可靠性。但停电后,存贮器中数据不能保存,每次通电,必须重新给存贮器装载编程数据。通常配置数据存放在EPROM、EEPROM或计算机中,系统开机时或需要时,由FPGA内初始化逻辑提供了在加电时自动加载配置数据至的SRAM中。用户也可以控制加载过程,在现场修改器件的逻辑功能,即所谓的现场编程。SRAM存储单元的数据一旦确定,门阵列的逻辑关系也就确定了。

查找表型的FPGA是用查找表实现多种组合逻辑功能。查找表是静态存储器SRAM构成的函数发生器,电路是由NMOS管构成的逻辑函数发生器。A、B是两个输入变量,F是输出逻辑函数。输出和输入的逻辑关系是由一组编程控制代码M0~M3决定,M0~M3为编程静态存储单元SRAM中的数据,通过向编程存储单元M0~M3写入不同数据, 查找表得到不同输入和输出的逻辑关系。当M0M1M2M3=1100时, 若AB=10, T1和T2导通, F=1; 若AB=01, T3和T4导通, F=1; 若AB=11或AB=00时, 则4条支路皆不导通, F=0; 因此F的逻辑表达式为F=AB+AB=A⊕B。表4.1是 M0~M3为不同取值时输入与输出的逻辑关系。

同理,多变量的逻辑函数发生器,都可通过查找表的方式进行设计。三变量函数发生器是由5位控制代码指定,四变量的函数发生器由16位控制代码指定。该组合逻辑单元的时延是固定的,与实现的逻辑函数的复杂性无关。

上述查找表类型的逻辑函数发生器只能产生组合逻辑功能,在此基础上再增加触发器,便可构成既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元电路。FPGA就是由许多这样的基本逻辑单元来完成各种复杂的逻辑功能。

FPGA中有许多可编程多路选择器实现其功能选择。与查找表的工作情况一样,可编程多路选择器对信号的选择也是通过编程存储单元中的数据来控制门阵列中门的开和关, 从而实现对多输入信号的选择输出。