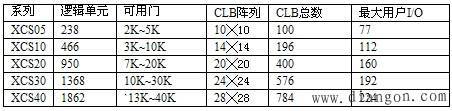

表1 Spartan系列产品主要性能

一、可编程逻辑模块CLB

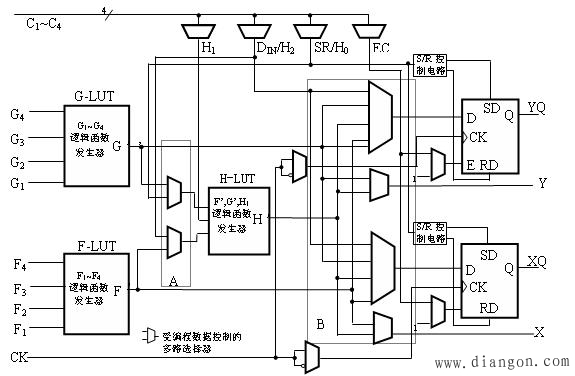

CLB是FPGA的基本逻辑单元电路,它能实现绝大多数的逻辑功能。CLB简化原理图如图1所示,CLB由组合逻辑函数发生器,即查找表LUT、触发器、编程数据存储单元和一些内部控制的数据选择器等电路组成。

图1 CLB的简化原理框图

CLB的组合逻辑发生器部分采用3个16×1的存储器查找表来实现组合逻辑函数,查找表的工作原理如前节所述。其中两个是四输入逻辑功能发生器F查找表(F-LUT)和G查找表(G-LUT),每个能提供四个独立输入信号的任何逻辑函数。它们各有16个编程数据存储单元,实现的逻辑功能由16个编程数据存储单元写入的数据决定。第三个函数功能发生器H-LUT能实现三输入变量的任意函数逻辑功能。其中两个输入端由A组数据选择器编程决定,这些输入可以来自于F和G的输出,也可以来自于CLB的外部输入H0和外部输入H2。第三个输入总是来自CLB的外部输入H1。因而,3个逻辑函数发生器的两级组合,CLB能实现高达九个输入变量的某些函数。这三个查找表能联合起来完成任何单个五输入变量的逻辑功能。作为查找表来实现的函数发生器,传播延时与实现的函数无关。

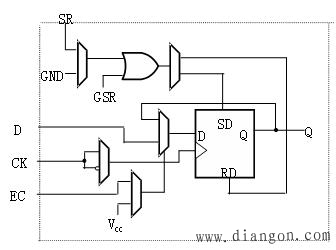

图2 CLB的存贮单元结构

来自函数发生器的信号也可以在查找表输出端退出CLB。F和H可以由可编程数据选择器编程接到X输出,G和H可接到Y输出,实现组合逻辑功能。

CLB可以传递组合逻辑的输出到互连网络,也可以在一个或两个触发器中存贮组合逻辑的结果或其它输入数据,并把它们输出同样连接到互连网络。每个CLB有两个边沿触发的D触发器,D触发器被利用来存贮组合逻辑发生器的输出。D触发器和组合逻辑发生器也能被独立应用。存贮单元数据输入是B组数据选择器编程决定的。CLB的存贮单元结构如图4所示。它由任何H-LUT驱动D触发器。两个触发器有一个可由用户规定极性为上升沿或下降沿的公共时钟CK。两个D触发器共用CLB的内部控制信号SR,通过各自的S/R控制电路,分别对两个触发器异步置位和复位。时钟使能也可通过选择器选择直接受CLB内部控制信号EC控制或接高电平。这两个D触发器都能被在上电或重配置时的全局置位/复位线初始化信号GSR控制。两个触发器分别从XQ和YQ输出,XQ和YQ是CLB的时序逻辑输出端。

CLB内部信号H1、DIN/H2、SR/H0、EC由CLB的四个控制信号输入端C1~C4通过四个数据选择器转换而成的。C1~C4中任意输入信号能控制任意个4个内部控制信号。

CLB的多功能性使系统速度有很大的改善。除此以外,设计工具软件能独立处理每个函数发生器。这种灵活性提高了单元的利用率。

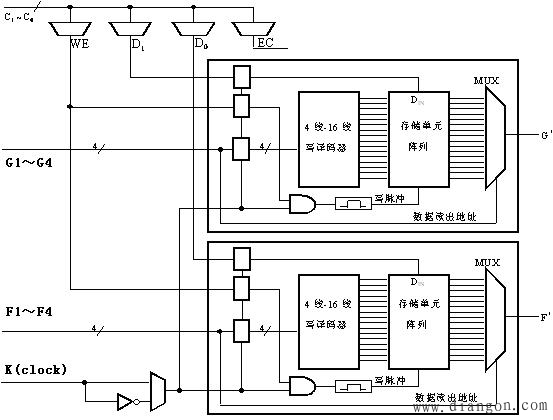

CLB除了实现组合逻辑和时序逻辑功能外,函数发生器G和F的编程数据存储单元还可构成读/写存储器使用。一个CLB可以构成两个容量为16×1位的RAM或一个32×1位RAM,函数发生器G的编程数据存储单元还可设置为16×1位的双口RAM(可以同时进行读操作和写操作)。以CLB构成两个16×1位单口RAM为例,其原理框图如图3所示。CLB作为RAM使用时,控制信号功能将有所变化,时钟脉冲K作为RAM的写入信号,H1、DIN/H2和SR/ H0变为两个数据输入端D0、D1和写使能输入,G1~G4和F1~F4分别为两个RAM的地址信号,G′、F′为两个RAM的数据输出。写入时,地址信号G1~G4、F1~F4经写地址译码器译码,选通相应的存储单元,在写时钟K和写使能WE的控制将数据D0、D1分别写入G和F的存储单元;读出时,读地址信号通过数据选择器,直接选通对应地址单元的存储数据,数据便可从RAM中立即输出。

图3 CLB构成两个16×1位单口RAM的原理框图

二、输入输出模块IOB

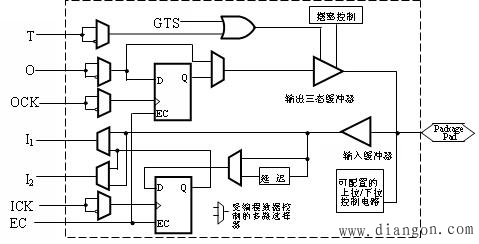

用户可编程IOB提供外部引脚和内部逻辑功能之间的接口。每个IOB控制一个封装引脚,并能被设置为输入、输出和双向工作模式 。每个I/O单元具有两个触发器、输入门限检测缓冲器、三态输出缓冲器、两根时钟输入线及一组程序控制存储单元。SPARTAN系列的IOB简化原理框图如图所示。

当I/O引脚作为输入时,能被配置为直接输入或由输入寄存器输入。IOB的输入信号通过输入缓冲器,能直接由I1、I2输入到内部逻辑电路,或由触发器寄存后输入至内部逻辑电路。每个IOB的输入缓冲器带有阀值检测,可将施加到封装引脚上的外部信号转换成内部逻辑电平,IOB的输入的阀值可编程为TTL电平或CMOS电平。缓冲后的输入信号驱动存储单元的数据输入。输入到寄存器前可以选择延时几个纳秒,由于延时使能,可使输入触发器的建立时间增加,足够的延时用于满足外部引脚上数据保持时间的要求。IOB数据输入通道每一个有一拍的延迟或者延迟是缺省的。这个增加的延迟保证了时钟通过任何全局时钟缓冲器的一个零保持时间。全局缓冲器用于输入寄存器建立时间。

当I/O引脚作为输入时,能被配置为直接输入或由输入寄存器输入。IOB的输入信号通过输入缓冲器,能直接由I1、I2输入到内部逻辑电路,或由触发器寄存后输入至内部逻辑电路。每个IOB的输入缓冲器带有阀值检测,可将施加到封装引脚上的外部信号转换成内部逻辑电平,IOB的输入的阀值可编程为TTL电平或CMOS电平。缓冲后的输入信号驱动存储单元的数据输入。输入到寄存器前可以选择延时几个纳秒,由于延时使能,可使输入触发器的建立时间增加,足够的延时用于满足外部引脚上数据保持时间的要求。IOB数据输入通道每一个有一拍的延迟或者延迟是缺省的。这个增加的延迟保证了时钟通过任何全局时钟缓冲器的一个零保持时间。全局缓冲器用于输入寄存器建立时间。

当I/O引脚作为输出时,输出信号由O端进入IOB模块,经选择器选择是否反相后,可被编程为直接输出或由输出寄存器输出至-个可编程的三态输出缓冲器。三态输出缓冲器的使能控制信号T能被编程定义为高电平或低电平有效。与FLEX 10K器件一样,三态输出缓冲器还具有可控转换速率,即输出摆率控制。

GTS是全局三态线强迫所有输出为高阻态,除了非边界扫描有效或工作在外界测试状态。

输入寄存器和输出寄存器共用时钟使能EC,但它们有各自的时钟信号ICK和OCK,且都能被编程为上升沿或下降沿触发。

可编程的上拉/下拉控制电路用于将没用到的引脚拉至VCC或GND电平, 以减少引脚悬空增加的附加功耗和系统噪声。

图4 IOB简化原理框图