器件编程需要满足一定的条件,如编程电压、编程时序和编程算法等。传统的编程技术是将PLD插在编程器上进行,比如简单PLD大多使用这种方式编程。目前,许多新型的CPLD/FPGA的编程采用了在系统可编程技术,在系统可编程技术是指未编程的器件可以直接焊接在印制电路板上进行编程或反复编程的能力。编程既不需要使用编程器,也不需要将它从电路板上取下,用户通过计算机和专用的编程电缆,可以对目标器件的逻辑功能进行随时方便地修改,简化了PLD器件的编程和目标系统的升极维护工作。我们在前两节举例介绍的CPLD和FPGA都具有在系统可编程特性。由于工艺不同,不同工艺的在系统可编程器件表现出不同的性能。基于乘积项的CPLD采用EPROM或E2CMOS工艺,如LATTICE公司的ispLSI 1016器件的可编程存储单元均为E2CMOS结构,编程过程就是把编程数据写入E2CMOS单元阵列的过程。而基于查找表的CPLD和FPGA,可编程存储单元为SRAM结构,SRAM中的数据理论上允许在器件被烧制以后可被无限次加载和修改,因此不仅具有在系统可编程性能,而且具有无限次动态重编程的功能。但是SRAM工艺的可编程单元掉电后数据丢失,因此需外部存储器,每次上电需要重新编程。本文主要介绍具有ISP特性的FPGA/CPLD的编程。

一、编程原理简介

下面以FPGA为例进行介绍PLD的编程原理。

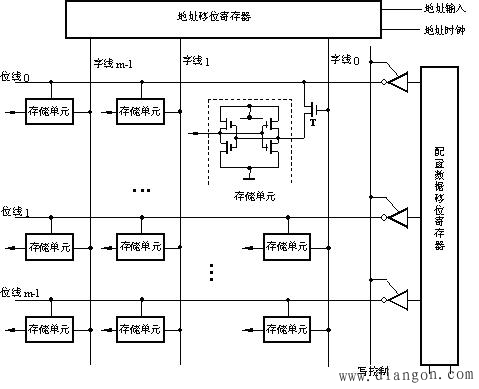

编程数据存储单元以阵列形式分布在FPGA中,编程数据存储单元阵列结构如图1所示。存储单元为5管SRAM结构, 只有一根位线。其中T管为本单元控制门,由字线控制。数据以串行方式移入移位寄存器,而地址移位寄存器顺序选中存储单元的一根字线,当某列字线为高电平时, 该列存储单元的T管导通,从而与位线接通,在写信号控制下将数据移位寄存器中一个字的数据通过各列位线写入该列存储单元。

编程数据按照一定的数据结构形式组成数据流装入FPGA中,编程数据流由开发软件自动生成。开发软件将设计转化成网表文件,它自动对逻辑电路分区、布局和布线和校验FPGA的设计,然后按PROM格式产生编程数据流并形成编程数据文件,最后还可将编程数据文件存入PROM中。

图1 编程数据存储单元阵列结构

二、编程模式

FPGA和CPLD器件的编程模式分为两大类:主模式和从模式。主模式是由起主导作用的FPGA或CPLD器件引导编程操作过程。而从模式由计算机、微处理器或其它主导可编程器件控制编程的过程。根据数据线的多少将编程分为并行模式和串行模式两类。这些不同分类模式相互组合可以形成主串模式、主并模式、从串模式和从并模式等多种模式。

另外,除了对单个的在系统可编程器件能够进行在系统编程外,还可以将印制电路板上的多个在系统可编程器件以串行的方式连接起来,一次完成多个器件的编程。这种编程模式被称为菊花链编程模式。

三、编程流程

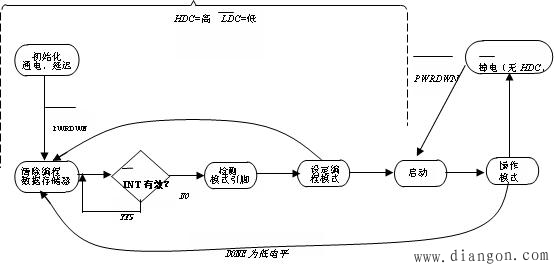

图2 FPGA器件的编程流程

FPGA器件的编程流程如图2所示。编程开始后,在加电和编程命令下,内部复位电路被触发,开始清除编程数据存储器。在INT为高电平时,电路自动测试MODE引脚状态,以确定装载模式。然后启动数据读入操作。编程开始时, 编程数据以一段起始码开头,其中包括编程数据的长度计数,接着便是设计文件的编程数据。当存储器初始化后所加的编程时钟总数等于编程数据的长度计数值时,数据装完,DONE被置为高电平,电路开始进入用户状态。