两个多位二进制数相加时,除了最低位以外,其他每一位相加时都需要考虑低位的进位,即将加数、被加数和低位的进位3个数相加,这种加法运算称为全加运算,实现全加运算的电路叫做全加器。

全加器的真值表如表1所示。A、B、CI分别为加数、被加数和低位的进位,S为本位和输出,CO为向相邻高位的进位输出。

表1 全加器真值表

| 输入 | 输出 | |||

| A | B | CI | CO | S |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

根据真值表写出输出逻辑函数式:

|

|

(1) |

|

|

(2) |

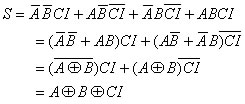

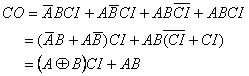

将函数式进行化简和转换

|

|

(3) |

|

|

(4) |

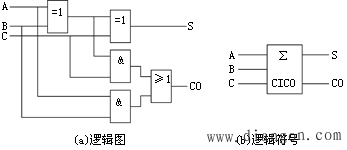

画出全加器的逻辑图,如图1所示。

|

| 图1 全加器 |