前面讲过,半加器实现两个1位二进制数相加时不考虑低位的进位,输出变量只有两个(加数和被加数),而全加器实现两个1位二进制数相加时则考虑低位的进位,输入变量有3个(加数、被加数和低位的进位)。

多位二进制数相加的特点是:最低位时两个数最低位的相加,不需考虑进位。其余各位都是3个数相加,包括加数、被加数和低位送来的进位。任何位相加都产生本位和与向高位的进位两个结果。

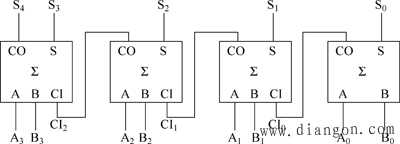

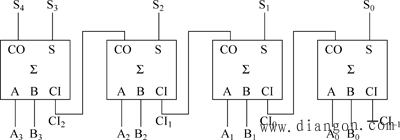

因此要进行多位二进制数相加,最简单的方法是将多个1位加法器进行级联,称为串行进位加法器。图1与图2所示都是4位串行进位加法器。图1所示电路中最低位都是半加器,其余各位是全加器,图2所示电路中都是全加器,最低位全加器的CI端接0。从图中可见,两个4位相加数A3A2A1A0和B3B2B1B0的各位同时送到相应全加器的输入端,进位数串行传送,相加的结果是CO,S3S2S1S0。1位加法器的个数等于相加数的位数。

|

| 图1 4位加法器电路(最低位是半加器) |

|

| 图2 4位加法器电路(最低位是全加器) |

串行进位加法器的优点是电路比较简单,缺点是速度比较慢。因为进位信号是串行传递,最后一位的进位输出CO3要经过4位全加器传递之后才能形成。如果进位增加,传输延迟时间将更长,工作速度更慢。

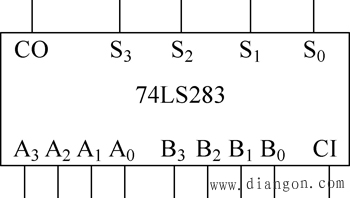

为了提高速度,人们又设计了一种多位数快速进位(又称超前进位)的加法器。所谓快速进位,是指加法运算过程中,各级进位信号同时送到各位全加器的进位输入端。现在的集成加法器大多采用这种方法。74LS283是一种典型的快速进位的集成4位二进制加法器。图3所示为74LS283加法器的图形符号。

|

| 图3 74LS283型4位加法器的图形符号 |

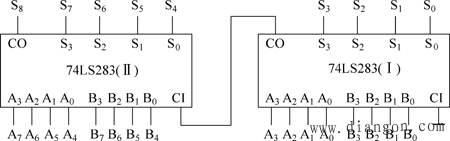

一片74LS283只能进行4位二进制数的加法运算,将多片74LS283进行级联,就可扩展加法运算的位数。用2片74LS283组成的8位二进制数加法电路如图4所示。

|

| 图4 8位二进制数加法器电路 |