要提高TTL门电路的工作速度,必须对电路加以改进。显然,影响门电路开关速度的一个重要因素是晶体管饱和与截止相互转换的时间。为减小这一时间,可采取以下措施。

① 减轻晶体管的饱和深度,甚至使输出级晶体管不饱和;

② 设法使晶体管基区的存储电荷尽快消散。

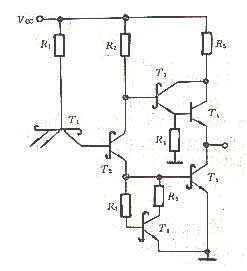

图 STTL与非门

由此出发,人们设计了抗饱和TTL与非门,如左图所示。它与典型TTL与非门相比有两点改进。第一,用带肖特基势垒二极管(SBD)的三极管来代替典型TTL与非门中所有可能在饱和状态下工作的晶体管 ![]() 、

、 ![]() 、

、 ![]() 和

和 ![]() ;第二,增加了一个由晶体管

;第二,增加了一个由晶体管 ![]() 、电阻

、电阻 ![]() 和

和 ![]() 构成的有源泄放电路来代替典型TTL与非门中

构成的有源泄放电路来代替典型TTL与非门中 ![]() 的发射极电阻

的发射极电阻 ![]() 。它们的作用分述如下。

。它们的作用分述如下。

1. SBD三极管的作用。

SBD三极管的等效电路如右图所示,它是由SBD跨接在三极管基极和集电极之间所得到的一种三极管。SBD正向压降比一般硅二极管小,仅有0.3~0.4V。当三极管截止、放大或刚进入饱和时,SBD均反偏截止,输入电流全部流入基极形成 ![]() 。SBD的接入不会影响三级管的开启时间。随着三极管饱和,集电结变为正偏。当

。SBD的接入不会影响三级管的开启时间。随着三极管饱和,集电结变为正偏。当 ![]() 0.3V时,SBD导通,由于三极管仅在浅饱和状态下工作,从而减少了电荷存储的时间。

0.3V时,SBD导通,由于三极管仅在浅饱和状态下工作,从而减少了电荷存储的时间。

2. 有源泄放电路的作用

u 加速 ![]() 管由截止到导通的过程 在STTL电路中,当输入电压由低电平变为高电

管由截止到导通的过程 在STTL电路中,当输入电压由低电平变为高电

平时, ![]() 由截止转为导通。由于

由截止转为导通。由于 ![]() 、

、 ![]() 的存在,使

的存在,使 ![]() >

> ![]() ,故

,故 ![]() 将先于

将先于 ![]() 导通。此时,由于

导通。此时,由于 ![]() 尚未导通,故

尚未导通,故 ![]() 射极电流的绝大部分都注入

射极电流的绝大部分都注入 ![]() 的基极。由此说明,有源负载的引入加速了

的基极。由此说明,有源负载的引入加速了 ![]() 的到通过程。

的到通过程。

u 加速 ![]() 管由导通导截止的转换过程 在STTL电路中,当输入电压由高电平变为

管由导通导截止的转换过程 在STTL电路中,当输入电压由高电平变为

低电平时, ![]() 截止,

截止, ![]() 和

和 ![]() 也将随之截止。但由于

也将随之截止。但由于 ![]() 的基极和集电极分别通过

的基极和集电极分别通过 ![]() 和

和 ![]() 接至

接至 ![]() 基极,故在

基极,故在 ![]() 基区存储电荷消耗完毕之前,

基区存储电荷消耗完毕之前, ![]() 发射结仍为正偏,因而

发射结仍为正偏,因而 ![]() 仍处于导通状态,又因

仍处于导通状态,又因 ![]() 的基极无泄放电阻,所以

的基极无泄放电阻,所以 ![]() 必定比

必定比 ![]() 晚一些截止。于是

晚一些截止。于是 ![]() 基区中的存储电荷可通过导通的

基区中的存储电荷可通过导通的 ![]() 进行泄放。而在典型的TTL与非门中,

进行泄放。而在典型的TTL与非门中, ![]() 基区中的存储电荷只能通过

基区中的存储电荷只能通过 ![]() 泄放,显然STTL的

泄放,显然STTL的 ![]() 基区电荷的泄放要比典型TTL电路快得多,从而加速了

基区电荷的泄放要比典型TTL电路快得多,从而加速了 ![]() 的截止过程。

的截止过程。

在STTL门电路的基础上,又相继研制出低功耗肖特基箝位TTL(简称LSTTL)电路和性能更为优良的先进的肖特基箝位TTL(简称ASTTL/ALSTTL)电路。(有兴趣可查阅有关的器件手册)

TTL集成门电路除与非门外,还有与门、非门、或门、或非门、与或非门、异或门等。此外,还有为提高驱动能力而设计的驱动器(也称功率门),以及主要起隔离作用的缓冲门等电路,都不再一一讨论。