OC门虽能实现多个门的输出并联使用,但由于在电源与门的输出之间串入了较大的电阻,因此OC门的负载能力及工作速度都有所降低。

⑴用高阻抗状态实现多个TTL门输出端并接

TTL与非门电路的V3和V4构成推拉式输出级。当输入数字信号,与非门处于正常工作状态时,V3和V4同时处于截止状态,这就意味着两个开关同时断开,既不与电源VCC相连,也不与地相连,这时的TTL门具有高阻抗状态。显然允许这样的门电路输出并接。这是从寻求新状态来解决门的并联使用问题。它较之OC门更简单、工作速度高、负载能力强。在数字系统和计算机中都采用了这种方法。

⑵TTL三态门的实现

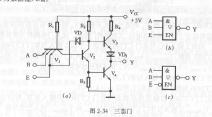

要使V3 与V4同时处于截止,即要求V3 与V4的基极同时加低电平。也就是与非门的输入端若有一个为低电平,则V4必然截止;但是按原来电路结构却又必然使V3导通,达不到同时截止的要求。若能将V4基极也同接于低电平,V3与V4同时截止就能实现。图1(a)所示三态门电路即为这样的结构。图中E为控制端,A、B为数据输入端。

图1 三态门

(a)电路结构;(b)高电平使能三态门符号;(c)低电平使能三态门符号。

在这个电路中,V3基极经二极管VD连到E端。当控制端E=0时,V2和V4截止。同时,二极管VD正偏导通,将V3的基极钳位在低电平,使V3也处于截止状态,从而实现了V3和V4同时截止。输入端E为使能控制端,E=0时与非门处于高阻状态。此门的输出除高电平、低电平之外,还有一个高阻状态,故称为三态输出(three state简称TS)门。

图1(a)电路在E=1时为与非门的工作状态,所以称为控制端高电平有效(使能),其符号如图1(b);也可以设计为低电平有效的情况,其符号如图1(c)所示,高电平控制的三态与非门的真值表如下

高电平使能的三态与非门真值表

|

E |

A |

B |

Y |

|

0 |

x |

x |

高阻 |

|

1 |

0 |

0 |

1 |

|

0 |

1 |

1 | |

|

1 |

0 |

1 | |

|

1 |

1 |

0 |

三态的符号是在普通门符号输出端的框内加上“▽”。图1中符号内的“EN”表示“使能关联”控制端,若后有标号(ENm)则表示只对于标号m的相应端点有使能关系。

同OC门一样,有各种不同逻辑功能的三态门,诸如三态与门,三态非门等。

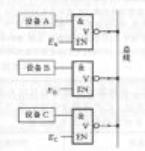

⑶用三态门实现总线结构

在数字系统或计算机中为减少连线数目,希望能在同一条导线上分时传递若干门路信号,这可以用三态门来实现。

当三态门输出端处于高阻状态时,对整个电路系统如同没把它们接入一样。利用三态门的性质可以实现不同设备与总线间的连接控制,这在计算机系统中尤为重要。如图2所示,有三个设备A、B、C共用一条数据总线(BUS),为了使电路能正常工作,必须使所有三态门在任何时刻只有一个门处于工作状态,而其余门都处于高阻状态。也就是说,对各个三态门采用分时控制的方法,使各三态门的控制端轮流为1,而且任何时刻仅有一个控制端为1,其他所有设备的控制信号为0,就能把各个门的输出信号轮流送到总线上而互不干扰,这种联接方式习惯上称为总线结构。

图2 三态门的应用

三态输出门还经常做成单输入、单输出的总线驱动器,并且输入与输出有同相和反相两种类型。利用三态输出门电路还能实现数据的双向传输。