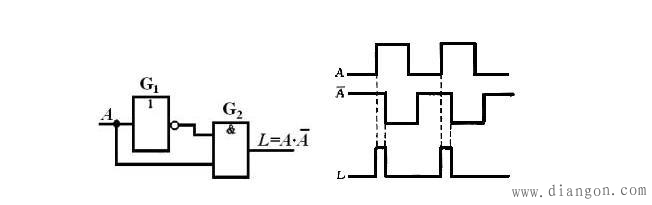

首先来分析下图所示电路的工作情况,可以建立竞争冒险的概念。

在图中,与门G2的输入是A和两个互补信号。由于G1的延迟,的下降沿要滞后于A的上升沿,因此在很短的时间间隔内,G2的两个输入端都会出现高电平,致使它的输出出现一个高电平窄脉冲(它是按逻辑设计要求不应出现的干扰脉冲),见图中的波形部分所示。与门G2的2个输入信号分别由G1和A端两个路径在不同的时刻到达的现象,通常称为竞争,由此而产生输出干扰脉冲的现象称为冒险。

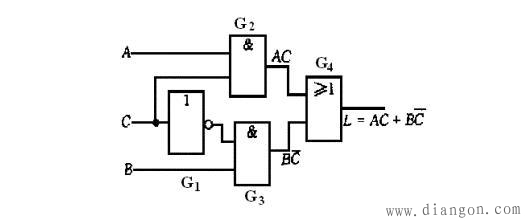

下面进一步分析组合逻辑电路产生竞争冒险的原因。

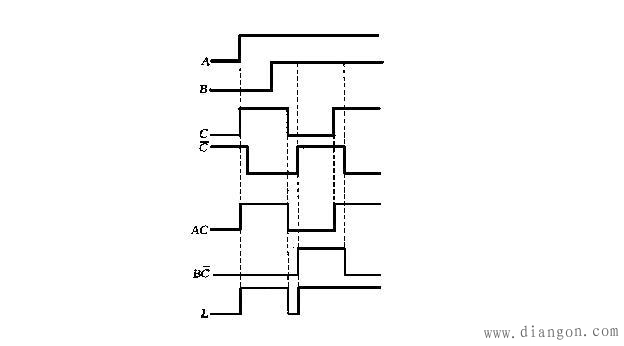

设有一个逻辑电路如上图所示,其工作波形如下图所示。它的输出逻辑表达式为。由此式可知,当A和B都为1时,L=1,与C的状态无关。但是,由波形图可以看出,在C由1变0时,C由0变1有一延迟时间,在这个时间间隔内,G2和G3的输出AC和同时为0,而使输出出现一负跳变的窄脉冲,即冒险现象。这是产生竞争冒险的原因之一,其他原因这里不作详述。

由以上分析可知,当电路中存在由反相器产生的互补信号,且在互补信号的状态发生变化时可能出现冒险现象。