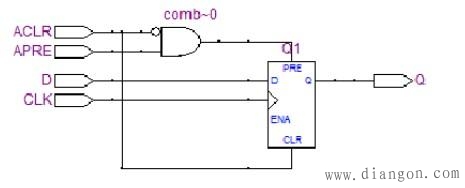

异步清零,异步置位触发器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY Dchu IS

PORT (

CLK : IN STD_LOGIC;

ACLR : IN STD_LOGIC;

APRE : IN STD_LOGIC;

D : IN STD_LOGIC;

Q :OUT STD_LOGIC

);

END;

ARCHITECTURE FFQ OF Dchu IS

SIGNAL

Q1:STD_LOGIC;

BEGIN

PROCESS (APRE,ACLR,CLK,Q1)

BEGIN

IF ACLR='1' THEN

Q1<='0';

ELSIF APRE='1'

THEN Q1<='1';

ELSIF CLK'EVENT AND CLK='1'

THEN Q1<=D;

END IF;

END PROCESS;

Q<=Q1; END FFQ;

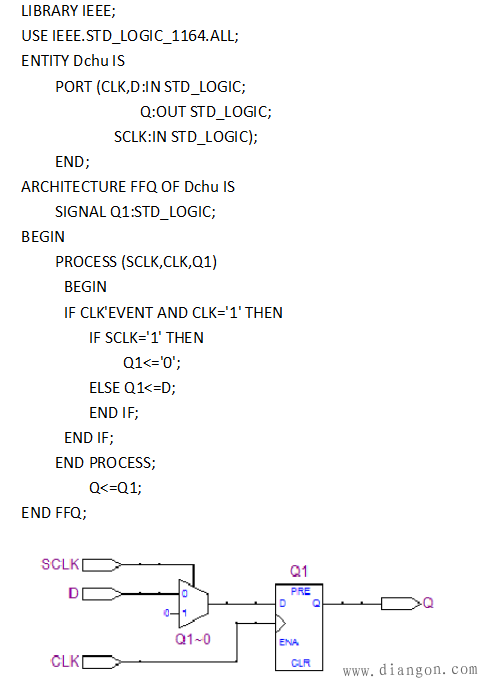

同步清零触发器