来源:本站

导读:目前正在解读《用VHDL描述二进制计数器》的相关信息,《用VHDL描述二进制计数器》是由用户自行发布的知识型内容!下面请观看由(

电工学习网 - www.9pbb.com)用户发布《用VHDL描述二进制计数器》的详细说明。

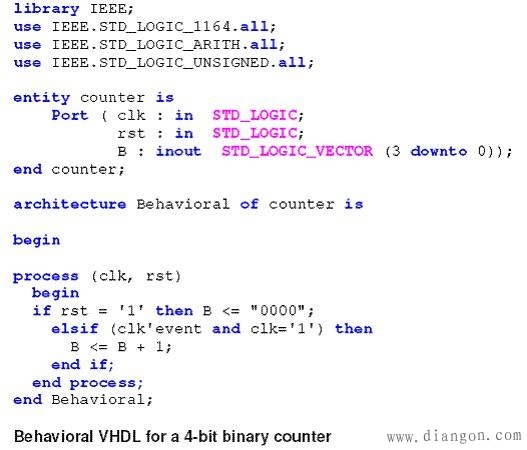

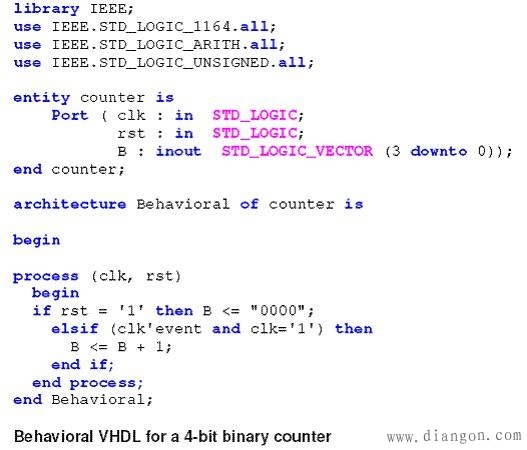

使用和结构和行为VHDL可以搭建出一个计数器电路。在结构性技术器设计中,先列举所有需要的触发器并作为其器件,然后描述出下一状态逻辑来驱动每个触发器的D输入(数据输入)。与行为性VHDL设计相比,这种设计方法非常冗长乏味,但是却能开发出很好的方案模型。

在任何标准的VHDL环境中,行为性计数器都可以很好的利用IEEE STD_LOGIC_UNSIGNED库。使用SLU库,所有的STD_LOGIC数据类型都可以使用标准算术操作符,从而使计数器设计相当简单。注意,计数器的计数输出是一个名称为B的矢量,且被定义为‘inout’类型,从而在赋值操作符两边都可以使用该矢量。

提醒:《用VHDL描述二进制计数器》最后刷新时间 2023-07-10 03:51:46,本站为公益型个人网站,仅供个人学习和记录信息,不进行任何商业性质的盈利。如果内容、图片资源失效或内容涉及侵权,请反馈至,我们会及时处理。本站只保证内容的可读性,无法保证真实性,《用VHDL描述二进制计数器》该内容的真实性请自行鉴别。