视频监控存储时间的规划

根据《规范》和建设方要求,视频保存时间为15天,实时25帧/秒监控,录像机远程显示与回放达到25帧/秒分辨率4CIF、CIF可选,本地显示时延≤0.5秒,远程浏览显示延时≤3秒。硬盘录像机以512K码流、重点部位按1.5M码流算,每台硬盘录像机所需硬盘数量计算如下表:

存储计算表

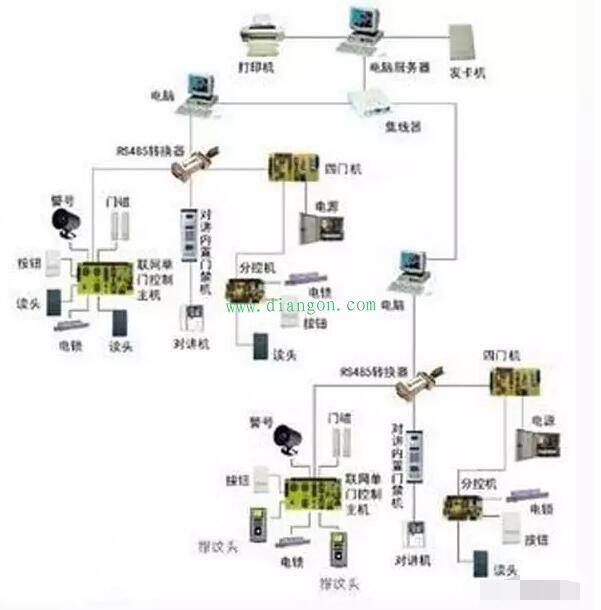

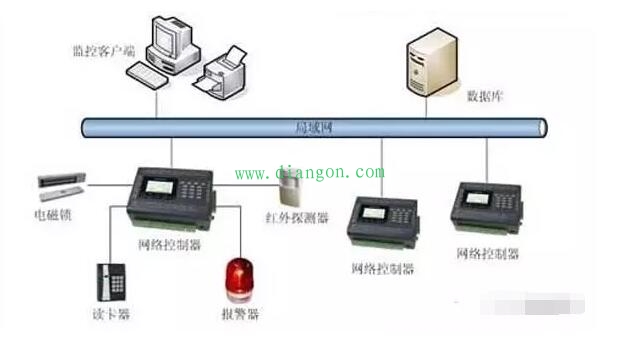

1、门禁视频智能系统的组成

视频电视监控系统是由摄像、传输、显示和控制四部分组成。是一种实时监控并可事后查询的防范能力极强的综合系统。广泛应用于各种不同的场合。通过摄像机及其辅助设备(云台)直接观看被受控场所的一切情况,并把前端摄像机获取的图像信号传送到控制中心,进行对视频信号的分配、切换、记录和重放等功能进行操作。

1、 摄像部分:摄像部分是电视监控系统的前沿部分,是整个系统的“眼睛”。

2、 传输部分:传输部分就是系统图像信号、声音信号、控制信号等的通道。

3、 控制部分:控制部分是整个系统的“心脏”和“大脑”,是实现整个系统功能的指挥中心。控制部分主要由总控制台、矩阵和矩阵键盘组成,本系统中的控制部分主要是指监控系统控制软件,现实软件控制。

4、 显示部分:显示部分由一台监视器组成。它的功能是将传送过来的图像一一显示出来。

2、门禁视频智能系统功能特点

1、 实时监控:可实时显示各监视点的情况。

2、 图像管理:可实现对图像的控制、回放、保存及其它管理。

3、 彩色、黑白系统混合设计,充分考虑了周界视频监看的严密性和景观视频图 像可观。赏性,整个系统经济实用,系统性能可靠。

4、 集成度、数字化程度高,易于系统扩展及远程传输。

5、 中文图形界面,操作简单。

6、 便于维修、维护及改造。

门禁系统与报警系统联动

报警系统其实就是门禁系统的一部分,门禁控制器本身具备报警功能。 当有人员强行开门或开门超时时,门禁控制器会自动输出报警信号,驱动现场声光报警器报警,同时报警信号实时上传至出租屋监控门禁报警监控平台,提醒管理人员及时查看现场报警情况。

3、门禁系统智能视频监控电路设计

主要介绍了基于FPGA的视频监控主机系统硬件设计中的多路视频采集电路、USB接口电路、串口转换及通信电路等电路的设计,单片机和FPGA的并行使用可以使数据传输更加协调,提高系统可靠性。该硬件系统能够实现视频信息的存储及传输,报警信息自动存储,USB信息拷贝,允许多路同时报警及远距离控制云台等功能,使得监控控制系统工作效率有了进一步的提高。

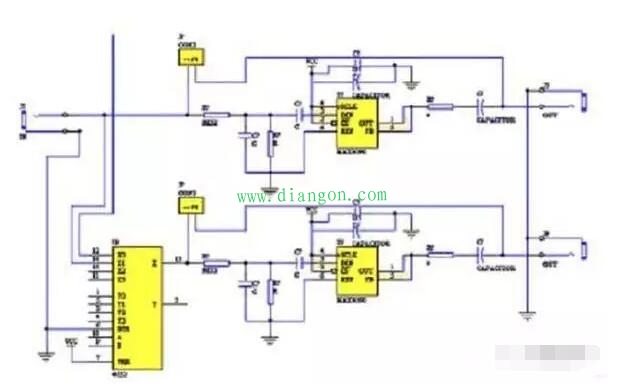

1、视频信号选择电路的设计

系统外部前端设备摄像机录入各个门禁场所视频,通过视频传输线路传到主机控制系统的视频信号选择电路视频信号。选择电路具有四路视频输入、四路视频输出,一个公共视频端输出。一方面视频信号经过MAX4090进行阻抗匹配后从四路视频输出,供管理人员查看门禁的现场活动情况,同时在公共视频端不仅可以输出一路视频,而且可以通过视频处理板对视频信息进行存储并通过网络传输视频信息;输出的视频信号通过FPGA的控制转换为可视信号并存储到PC中,同时FPGA可以不断检测视频警报信号量来触发报警信号。

如图所示为只有1路输入,1路输出并带有一路公共视频的电路图作为视频选择电路系统的讲解示意,J1为视频信号输入端,J5,J9为视频信号输出端.CON2为短路跳线对相应的通道进行连通与断开。当CON2断开时,相应的通道连通,视频信号从左边输入,经过匹配后右边输出;当CON2连通时,则视频信号输入后不能经过匹配处理而直接输出。然后利MAX4090用进行阻抗匹配进行多路视频的选择输出。该电路使用了交流耦合输出方式。从技术特征出发,将视频信号输出到媒体显示设备的最普遍方法是交流耦合,这使得接收电路可以在自己的输入端建立共模电平,该电平独立于输入视频信号的直流电平。一个75欧的串联电阻应该尽可能近地放在靠近输出端的位置,这有助于隔离从输出端产生的下行寄生干扰,并提供最佳的信号条件。

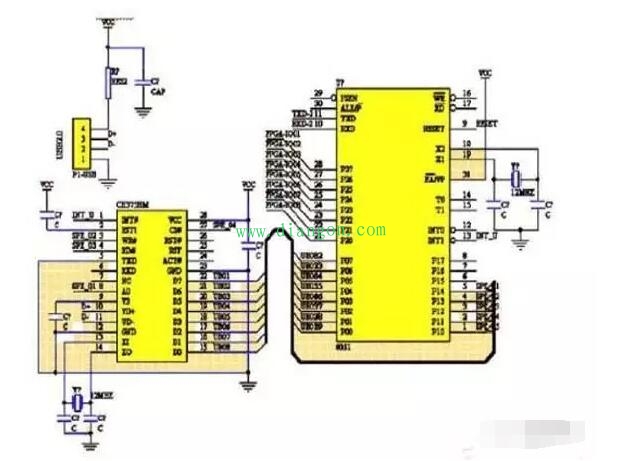

2、USB接口电路的设计

为了方便的使用USB摄像头及USB的数据下载通道,系统总需要设计USB接口电路。

USB电路如图所示,USB功能采用常见的CH375芯片作为USB借口控制芯片。CH375是一个USB总线的通用借口芯片,支持USB-HOST主机方式和USB-DEVICE/SLAVE设备方式。 在本地端,CH375具有8位数据总线和读、写、片选控制线以及中断输出,可以方便地挂接到单片机/DSP/MCU/MPU等控制器的系统总线上。在USB主机方式下,CH375 还提供了串行通讯方式,通过串行输入、串行输出和中断输出与单片机/DSP/MCU/MPU等相连接。CH375有串口和并口两种与单片机的连接方式,在本系统中,CH375 芯片是通过并行方式连接到副控制芯片的,CH375的 TXD引脚通过1千欧左右的下拉电阻接地或者直接接地,从而使CH375工作于并口方式。这种并行连接方式极大的提高了数据的传输速率。

3、FPGA的EPROM及单片机存储电路设计

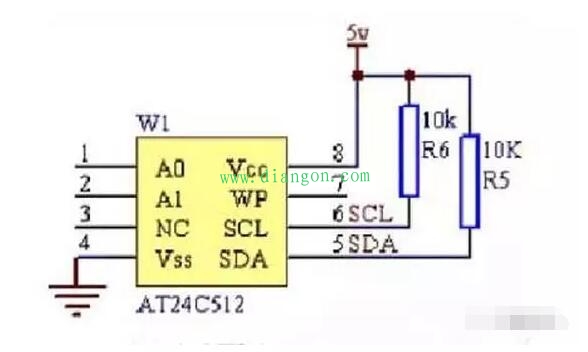

系统中使用了AT24C512EEPROM器件作为主要存储芯片,它的存储容量为512K及单片机对AT24C51系列E2PROM的读写操作完全遵守12C总线的主收从发和主发从收的规则。数据的传送由四部分组成:起始(START)条件、从机地址的发送、数据的传送和停止(STOP)条件。每一个时钟高电平中期间传送一位数据,而且在SCL线为高电平时SDA线上的数据必须保持稳定,否则将认为是一个控制信号。这样设计的优点体现在其简单性和有效性上。

如图所示电路,一般A0、A1、WP接VCC或GND,SCL、SDA接上拉电阻(上拉电阻的阻值可参考有关数据手册选择,通常可选5K到10K的电阻,本设计中选用的电阻阻值为10K)后再接单片机的普通I/O口,即可实现单片机对AT24C512的操作。在对AT24C512开始操作前,需要先发一个8位的地址字来选择芯片以进行读写。其中要注意“10100”为AT24C512固定的前5位二进制;A0、A1 用于对多个AT24C512加以区分;R/W为读写操作位,为1时表示读操作,为0时表示写操作。AT24C512内部有512页,每一页为128字节,任一单元的地址为16位,地址范围为0000—0FFFFH。虽然FPGA芯片和单片机都有EEPROM读写的功能,但并不是说它们拥有各自独立的EEPROM 芯片,而是两片单片机共同复用EEPROM芯片。如果两个芯片同时读写EEPROM芯片,则单片机肯定会产生死机现象,因此需要一个严格的机制保证不会出 现两片单片机同时读或者写EPROM芯片的现象。该机制称为EPROM复用关系,即采用一个握手信号协调两者的使用。

在视频选择电路中采用了交流耦合技术,这样设计有利于保持高清晰视频信号的传输。同时利用FPGA作为中央控制部分的,采用了并行的两块单片机 做为副控芯片,一块用于USB接口的数据控制与传输,另外一块用于其它接口操作和外部存储控制,既了协调视频信号的实时监控与传输,又能够保证FPGA的 处理不受到外部电路的影响,大大提高了系统的工作效率。