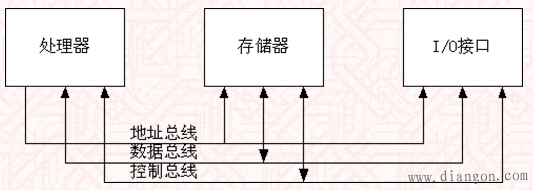

图1 微处理器系统的基本结构

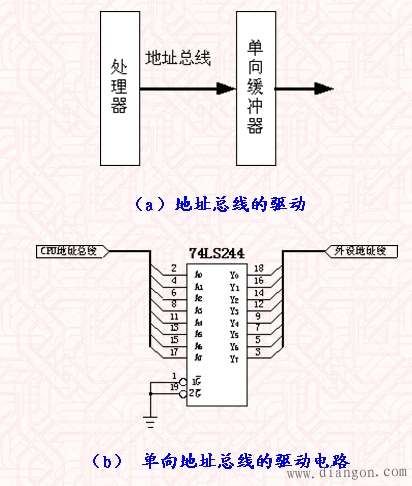

对于微处理器,地址信号是输出信号,它的作用是选择存储器或I/O接口的地址。当一个系统有较多的存储器单元或I/O接口需要选择时,需要地址信号提供较大的驱动能力,如所需的驱动能力大于微处理器的输出能力时,应对地址信号加驱动电路。地址总线的驱动如图2(a)所示,常用的器件有图2(b)所示的74LS244,它是一个单方向的缓冲器,能提供12 mA的电流驱动能力。其使能控制端为-G,当-G= 0时,电路的输出有效,当-G=1时电路的输出为高阻态。

图2 地址总线的驱动与驱动电路

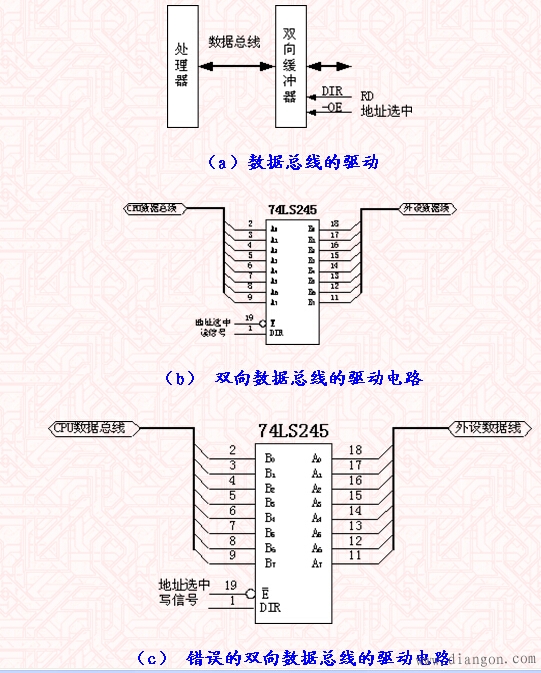

数据总线上传送的是指令和数据。在微处理器读取指令时,在数据总线上传送的是指令信息,指令从存储指令的存储器读出,送入微处理器进行处理。对于微处理器,此时的数据总线是输入信号。在读取或输出数据时,在数据总线上传送的是数据,这些数据将根据需要与存储器或I/O接口交换。在读取数据时,对于微处理器,此时的数据总线是输入信号。在输出数据时,对于微处理器,此时的数据总线是输出信号。因此数据总线是双向信号,根据读写控制信号,或读指令控制信号能判断其传输的方向。

很容易理解,当微处理器连接较多的存储器或I/O接口电路时,需要它提供较大的负载电流,因此需要提供总线驱动电路。但当微处理器连接较少的存储器或输出接口电路,而这些电路与微处理器的距离较远时,将有较大的电容负载,此时同样需要总线驱动电路。与地址总线的驱动电路不同的是,数据总线必须采用图3(a)所示的双向驱动电路,常用的器件有图3(b)所示的74LS245,与74LS244不同的是,它不但具有使能控制信号,还需方向控制信号。其使能控制端为-E,当-E= 0时,电路的输出有效,当-E=1时电路的输出为高阻态。DIR端决定传送方向,当 DIR=0时信号从B端流向A端,而当DIR=1时信号从A端流向B端。方向控制信号必须在读有效时起作用,当此信号有效时将存储器或I/O接口的数据送往微处理器。在写信号有效时微处理器的数据送往存贮器或I/O接口。

图3 数据总线的驱动与驱动电路

在使用双向缓冲器74LS245时必须考虑使能端和方向端的连接方法,通常使能端应在存储器或I/O接口被选中时起作用,而方向端则由读信号控制。在未选中存储器或I/O接口时双向缓冲器输出为高阻态,在选中存储器或I/O接口时,如为读信号有效,双向缓冲器的输出连接到数据总线上,将数据送往微处理器,而非读信号时数据从微处理器送出。非读信号有效包括了写信号有效或时序的其他状态,采用读信号作为方向控制端避免了时序在其他状态时双向缓冲器的输出连接到数据总线上而造成数据总线的冲突。

如采用图33(c)的方法,用写信号作为控制端,在写信号有效时数据从微处理器输出,在读有效及时序的其他状态时双向缓冲器的输出连接到数据总线上,而后者将造成数据总线冲突。

使能端的另一个连接方法是直接接低电平,此时无论地址是否有效,在发出读信号时都会将双向缓冲器的输出连接到数据总线上。这种方式适用于微处理器只连接一个总线驱动器的场合;如系统总线连接了多个总线驱动器,或连接一个总线驱动器,又直接连接了部分存储器或I/O接口时,则会造成数据总线冲突。

微处理器的控制信号提供了微处理器正常工作所需的系统时钟信号和复位信号。还提供了控制存储器或I/O接口的信号,包括了读写控制,存储器与I/O接口的区分,中断信号的处理,直接数据通道的处理。在这些信号的作用下微处理器能将数据送入存储器或输出接口,或者从存储器或输入接口读入数据。