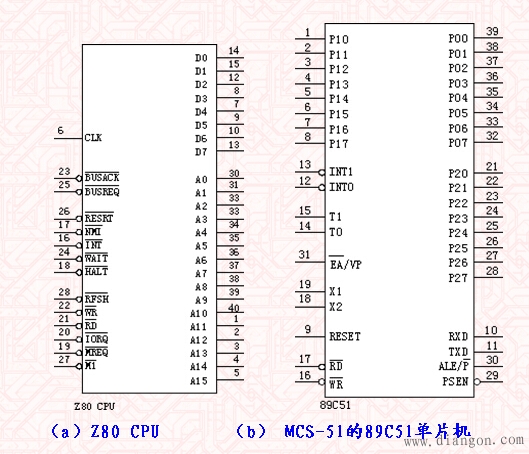

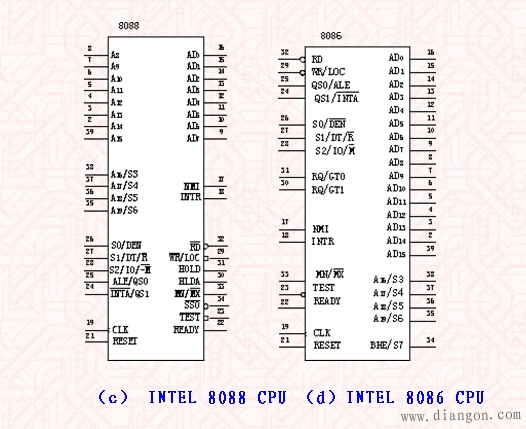

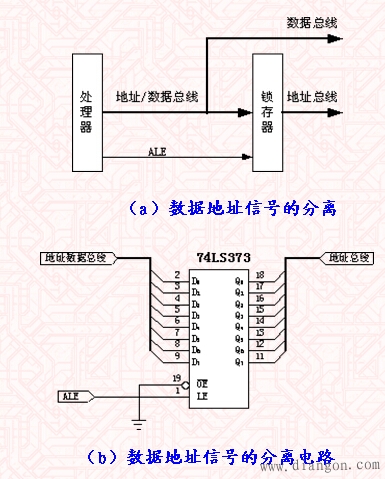

微处理器与存储器和I/O接口之间通过数据总线、地址总线和控制总线相连接。图1为常用的几种微处理器。在八位微处理器Z80 CPU中明显地可以区分出数据总线和地址总线。而微处理器INTEL 8086/8088和微控制器89C51由于封装的原因,不可能将所有的信号连接到外部,因此有一部分引脚具备两种功能,以便用有限的引脚产生更多的连接信号。这些引脚两种功能的选择可通过不同的方式来决定,一类引脚功能的选择是通过微处理器的时序来区分,另一类引脚的功能由微处理器的某个功能设置引脚来定义。在微处理器INTEL 8086/8088 以及微控制器89C51中,数据总线和地址总线就采用时序区分的方法,由引脚输出的为信号AD总线,当地址锁存信号ALE有效时此信号为地址信号,当读写控制信号或读指令信号有效时此信号为数据信号。为了在AD总线上分离出地址总线,通常采用如图2所示的锁存器74LS373,锁存信号LE在高电平时将D端的信号传输到Q端,在低电平时输入信号D不能传输到Q端,使能端-OE使输出有效。在作为地址锁存器使用时,其使能端-OE为低电平,输入信号D为微处理器的AD总线,锁存信号LE为微处理器的地址锁存信号ALE,当此信号有效时,将AD总线中的地址信息锁存,并从Q端输出。

图1 常用的微处理器

图2 地址总线的分离