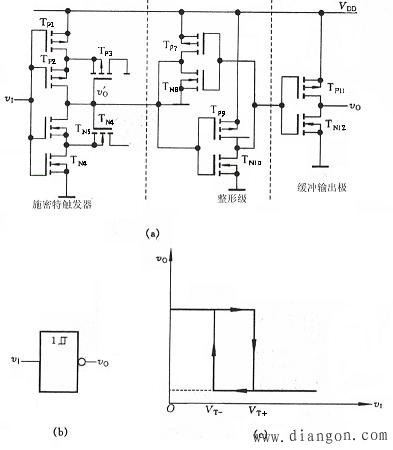

图1 CMOS集成施密特触发器电路 (a) 电路图 (b) 逻辑符号 (c) 传输特性曲线

图1 CMOS集成施密特触发器电路 (a) 电路图 (b) 逻辑符号 (c) 传输特性曲线由图1(a)可见,它由施密特电路、整形级和缓冲输出级组成。

1.施密特电路

施密特电路由P沟道MOS管TP1~TP3、N沟道MOS管TN4~TN6组成,设P沟道MOS管的开启电压VGS为VTP,N沟道MOS管开启电压VGS为VTN,输入信号vⅠ为三角波。

当vⅠ=0时,TP1、TP2导通,TN4、TN5截止,电路中vO'为高电平(vO'≈VDD),TP9截止,TN10导通,v"为低电平,使TP11导通,TN12截止,vO=VOH。v0"使TP7导通,TN8截止,维持vO'≈VDD,vO'的高电平同时使Tp3截止,TN6导通且工作于源极输出状态。即TN5的源极TN4的漏极电位vS5≈VDD-VTN6,该电位较高。

vⅠ电位逐渐升高,当vⅠ>VTN4时,TN4先导通,由于TN5其源极电压vS5较大,即使vⅠ>VDD/2,TN5仍不能导通,直至vⅠ继续升高直至TP1、TP2趋于截止时,随着其内阻增大,vO'和vS5才开始相应减少。

当vⅠ-VS5≥VTN5时,TN5导通,并引起如下正反馈过程:

|

vO'的低电平使TN6截止,TP3导通且工作于源极输出器状态,TP2的源极电压vS2≈0-VTP。

同理可分析,当vⅠ逐渐下降时,电路工作过程与vⅠ上升过程类似,只有当│vⅠ-vS2│>│VTP│时,电路又转换为vO'为高电平,vO=VOH的状态。

在VDD>>VTN +│VTP│的条件下,电路的正向阈值电压VT+远大于VDD/2,且随着VDD增加而增加。在vⅠ下降过程中的负向阈值电压VT-也要比VDD/2低得多。

由上述分析可知,电路在vⅠ上升和下降过程分别有不同的两个阈值电压,具有施密特电压传输特性。其传输特性如图10.9.3所示。

2.整形级

整形级由TP7、TP8、TP9、T10组成,电路为两个首尾相连的反相器。在vO'上升和下降过程中,利用两级反相器的正反馈作用可使输出波形有陡直的上升沿和下降沿。

3.输出级

输出级为TP11和TN12组成的反相器,它不仅能起到与负载隔离的作用,而且提高了电路带负载能力。

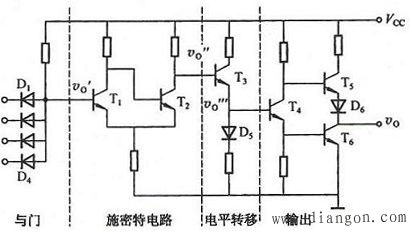

图2所示为4输入与非门(TTL)电路,图中D1~D4构成四输入二极管与门,T1、T2构成射级耦合双稳态触发器(施密特触发器),T3、D5是射级跟随器,完成电平转移,T4、T5、T6构成推拉式输出电路。

|

| 图2 四输入与非门施密特电路图 |