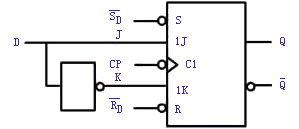

可以将JK触发器转换为D触发器,其逻辑图和逻辑符号如图1(a)和(b)所示。当D=1,即 ,

, 时,在CP的下降沿触发器翻转为(或保持)1态;当

时,在CP的下降沿触发器翻转为(或保持)1态;当 ,即

,即 ,

, 时,在CP的下降沿触发器翻转为(或保持)0态。

时,在CP的下降沿触发器翻转为(或保持)0态。

|

|

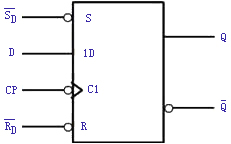

| (a)逻辑图 | (b)逻辑符号 |

| 图1D触发器 | |

由以上可知,某个时钟脉冲来到之后输出端Q的状态和该脉冲来到之前输入端D的状态一致,即

D触发器的逻辑状态表见表1。

| 表1 D触发器的逻辑状态表 | |||

| D |  |

|

功能 |

| 0 | 0 |  |

置0 |

| 1 | |||

| 1 | 0 |  |

置1 |

| 1 | |||

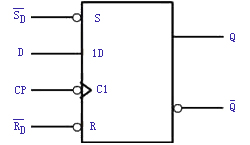

国内生产的D触发器主要是维持阻塞型(不在本书中讨论),如双上升沿D触发器74LS74、四上升沿D触发器74LS175等,它们在时钟脉冲的上升沿触发,逻辑符号如图2所示,在CP输入端不加小圆圈。

|

|

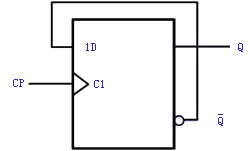

| 图2上升沿D触发器的逻辑符号 | 图3 D触发器转换为T触发器 |

也可将D触发器转换为T触发器,如图3所示。它的逻辑功能是每来一个时钟脉冲,翻转一次,即 ,具有记数功能。

,具有记数功能。