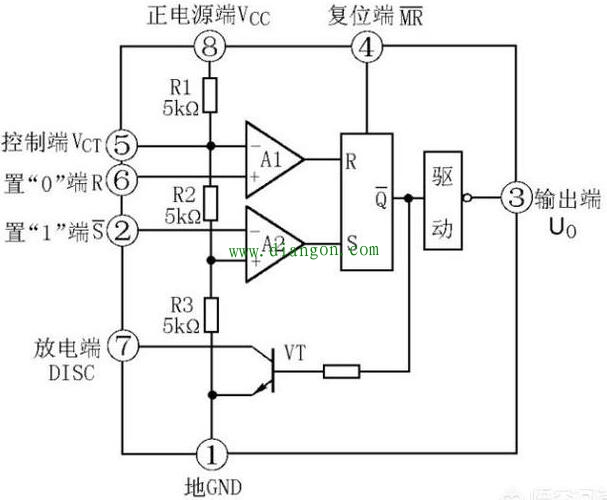

电阻R1~R3组成分压网络,为A1,A2两个电压比较器提供2/3Vcc和1/3Vcc两个基准电压。两个电压比较器的输出分别作为R-S触发器的置“0”信号和置“1”信号。输出驱动极和放电管VT受R-S触发器控制。

时基集成电路的基本工作原理是:当置“0”输入端R电压UR>=2/3Vcc时(US>=1/3Vcc),上限比较器A1输出端为“1”,使R-S触发器置“0”,电路输出Uo为“0”,放电管VT导通,放电端DISC为“0”;

当置“1”输入端电压US<=1/3Vcc时(UR<=2/3Vcc),下限比较器A2输出为“1”,使R-S触发器置“1”,电路输出Uo为“1”,放电管VT截止,放电端DISC为“1”;

当强制复位端为“0”时,Uo为“0”,DISC为“0”。电路的逻辑真值表见下表。

根据以上基本原理,只要给时基集成电路配置上接法不一的外围阻容元件等,便可构成多谐振荡器、单稳态触发器、双稳态触发器和施密特触发器等各种各样的应用电路。