1、反相加法运算电路

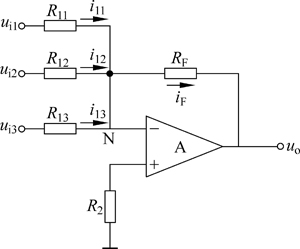

加法运算电路能实现多个模拟量的求和运算。图1所示为一个3个输入信号的反相加法运算电路。

|

|

图1 反相加法运算电路 |

根据“虚短路”和“虚断路”的原则,up=un=0。

节点N的电流方程为

| (1) |

| (2) |

对上式整理得

| (3) |

当RI1=RI2=RI3=R1时

| (4) |

当当RI1=RI2=RI3=RF时

| (5) |

平衡电阻R2=RI1//RI2//RI3//RF

2、同相加法运算电路

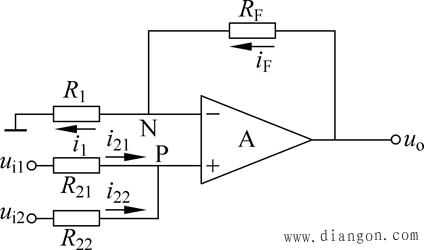

加法运算电路也可以采用同相输入的方式,图2是一个两个输入信号的同相加法运算电路。

|

| 图2 同相加法运算电路 |

根据“虚断路”的原则,iI=iF,即![]() ,整理得

,整理得

| (6) |

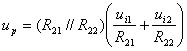

根据“虚断路”的原则,节点P的电流方程为i21+i22=0,即![]() ,整理得

,整理得

|

(7) |

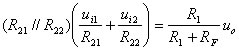

根据“虚短路”的原则,up=un。并结合式(6)和式(7)得

|

(8) |

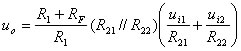

从而

|

(9) |

若R21=R22=R1=RF,则uo=ui1+ui2。

为了提高电路的共模抑制比和减小零漂,一般要求R21//R22=R1//RF。

3、减法运算电路

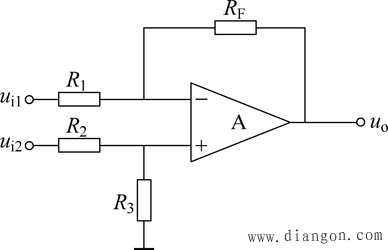

减法运算电路如图3所示,同相和反相输入端都有信号输入,则称为差动输入运算电路。

|

| 图3 减法运算电路 |

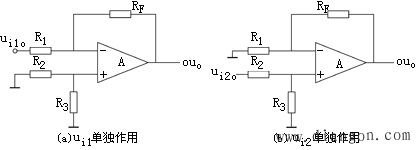

分析减法运算电路用叠加原理比较简单,图4(a)和图4(b)分别是输入信号ui1和ui2单独作用时的电路。

|

| 图4 运用叠加原理的减法运算电路 |

由图4(a)可知,ui1单独作用时电路为反相比例运算电路,输出电压为

| (10) |

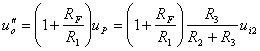

由图4(b)可知,ui2单独作用时电路为同相比例运算电路,由于电阻R3的分压作用,使同相输入端电位![]() ,所以输出电压为

,所以输出电压为

|

(11) |

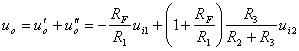

因此,ui1和ui2同时作用的输出电压为

|

(12) |

当R1=R2、R3=RF时,![]() 。

。

当R1=R2=R3=RF时,![]() 。

。