寄存器是一种存储二进制数码的时序电路组件,它具有接收和寄存二进制数码的逻辑功能。一个触发器可以存储1位二进制数,那么用n个触发器就可以存储n位二进制数码。

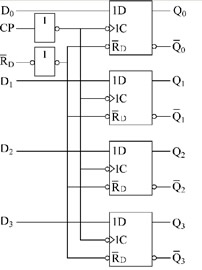

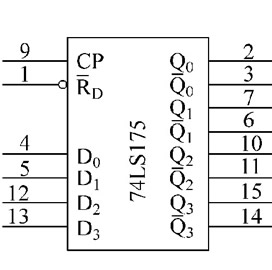

图1(a)所示是由D触发器组成的4位集成寄存器74LS175的逻辑电路,其图形符号如图1(b)所示。

由图1(a)可知,寄存器74LS175由4个下降沿触发的边沿D触发器组成,4个D触发器受到同一个时钟脉冲CP的控制,时钟脉冲CP的控制,时钟脉冲CP经过一个非门到达各触发器的时钟脉冲控制端,因此4个D触发器都在时钟脉冲CP的上升沿触发。D0~D3为数据输入端,Q0~Q3为数据输出端,![]() 为清零控制端。

为清零控制端。

|

|

| 图1(a) 逻辑图 | 图1(b) 图形符号 |

将需要存储的4位二进制数码送到数据输入端D0~D3,当CP端送入一个时钟脉冲,在CP脉冲的上升沿作用后,数据输入端的4位二进制数码将同时出现在4个触发器的输出端Q0~Q3。这种数据同时输入到寄存器的数据输入端,并且触发器中的数据同时出现在数据输出端的形式,叫做并行输入并行输出方式。当在清零端输入一个低电平则将各触发器的输出端都清零。表1所示为74LS175的逻辑功能。

| 表1 74LS175的功能表 |

| 清零 | 时钟 | 输入 | 输出 | 工作模式 | ||||||

| RD | CP | D4 | D1 | D2 | D3 | Q4 | Q1 | Q2 | Q3 | |

| 0 | × | × | × | × | × | 0 | 0 | 0 | 0 | 异步清零 |

| 1 | ↑ | D0 | D1 | D1 | D3 | D0 | D1 | D1 | D3 | 数码寄存 |

| 1 | 1 | × | × | × | × | 保持 | 数据保持 | |||

| 1 | 0 | × | × | × | × | 保持 | 数据保持 | |||