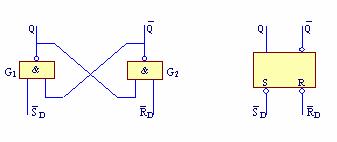

电路组成:两个与非门输入和输出交叉耦合(反馈延时)。如下图所示。

图1基本RS触发器逻辑电路和符号

(1)信号输入端:RD置0端(复位端);SD置1端(置位端)。非号表示低电平有效,在逻辑符号中用小圆圈表示。

(2)输出端:Q和Q,在触发器处于稳定状态时,它们的输出状态相反。

2.逻辑功能

(1)当RD=0,SD=1时,触发器置0。输入 ![]() 端称为置0端,也称复位端,低电平有效。

端称为置0端,也称复位端,低电平有效。

(2)当RD=1,SD=0,触发器置1。输入端 ![]() 称为置1端,也称置位端,低电平有效。

称为置1端,也称置位端,低电平有效。

(3)当RD=1,SD=1时,触发器保持原状态比不变。如果触发器原处于Q=0, Q=1的0状态,电路保持0状态不变;如果触发器原处于Q=1, Q=0的1状态,电路保持1状态不变。

(4)当RD=0,SD=0时,触发器状态不定,:输出 Q=Q=1这既不是1状态,也不是0状态。这会造成逻辑电路混乱。

在RD和SD同时由0变为1时,由于 G1和G2电气性能(延迟时间)上的差异,其输出状态无法预知,可能是0状态,也可能是1状态。

实际上,这种情况是不允许的。因此,基本的RS触发器有约束条件:

RD+RS=1

3.特性表

现态:是指触发器输入信号 (RD,SD端)变化前的状态,用Q n表示

次态:是指触发器输入信号变化后的状态,用Q n+1表示

特性表:触发器次态Q n+1与输入信号和电路原有状态(现态)之间关系的真值表。

表1 与非门组成的基本RS触发器的特性表

|

RD,SD |

Qn |

Qn+1 |

说 明 |

0 0 |

0 1 |

× × |

触发器状态不定 |

0 1 |

0 1 |

0 0 |

触发器置0 |

1 0 |

0 1 |

1 1 |

触发器置1 |

|

1 1 1 1 |

0 1 |

0 1 |

触发器保持原状态不变 |