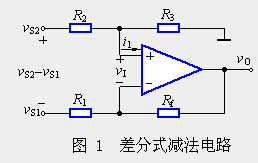

图1所示电路可以实现两个输入电压vS1、vS2相减,在理想情况下,电路存在虚短和虚断,所以有vI=0,iI=0,由此得下列方程式:

![]()

及 ![]()

由于vN=vP,可以求出 ![]()

若取 ![]() ,则上式简化为

,则上式简化为 ![]()

即输出电压vO与两输入电压之差(vS2–vS2)成比例,其实质是用差分式放大电路实现减法功能。

差分式放大电路的缺点是存在共模输入电压。因此为保证运算精度应当选择共模抑制比较高的集成运放。差分式放大电路也广泛应用于检测仪器中,可以用多个集成运放构成性能更好的差分式放大电路。

图1所示电路可以实现两个输入电压vS1、vS2相减,在理想情况下,电路存在虚短和虚断,所以有vI=0,iI=0,由此得下列方程式:

![]()

及 ![]()

由于vN=vP,可以求出 ![]()

若取 ![]() ,则上式简化为

,则上式简化为 ![]()

即输出电压vO与两输入电压之差(vS2–vS2)成比例,其实质是用差分式放大电路实现减法功能。

差分式放大电路的缺点是存在共模输入电压。因此为保证运算精度应当选择共模抑制比较高的集成运放。差分式放大电路也广泛应用于检测仪器中,可以用多个集成运放构成性能更好的差分式放大电路。

上一篇微分电路

下一篇反相求和式减法运算电路