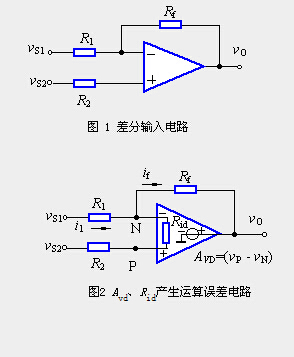

集成运放的AVD和Rid为有限值时,对运算电路将引起误差,现以图1所示的运算放大电路为例来讨论,用图2电路来等效。

由此可列出如下方程

解之可得 <?XML:NAMESPACE PREFIX = V />

其中 ![]()

当vS2=0,图1即为反相比例运算电路。此时上式变为

通常AVDRidR¢1>>Rf(R¢1+R2+Rid),利用近似公式(|x|<<1时 ![]() ),上式可化简为

),上式可化简为

![]()

闭环电压增益

反相比例运算电路的理想闭环增益为 ![]()

由此可得相对误差 ![]()

![]()

上式说明,AVD和Rid越大,AVF越接近理想值,产生的误差也越小。d<0说明实际值比理想值的绝对值小。按类似方法可以分析同相比例运算电路。