1. 维持阻塞触发器

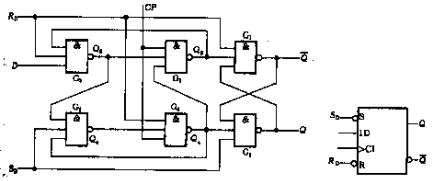

这是边沿触发器的一种电路结构形式,在TTL电路中常用该形式。下面给出维持——阻塞式边沿D触发器的逻辑图和逻辑符号。

维阻型触发器电路结构和逻辑符号

该触发器由6个与非门构成,其中G1和G2组成基本RS触发器。分析工作原理:

Ⅰ.  时,不论输入端D为何种状态,都会使

时,不论输入端D为何种状态,都会使 ![]() ,即触发器置1。

,即触发器置1。

时,不论输入端D为何种状态,都会使

时,不论输入端D为何种状态,都会使 ![]() ,即触发器置0。

,即触发器置0。

因此,SD 和RD 通常称预置端和清零端。

Ⅱ. 当触发器工作时,必须使 SD =RD =1 ,

(1)CP=0时,G3 和G4 封锁,其输出Q3 =Q4 =1,此时基本RS触发器处于保持状态,即 ![]() 状态不变。同时,由于Q3 至G5 和Q4至G6 的反馈信号将这两个门打开,因此可接收输入信号D,

状态不变。同时,由于Q3 至G5 和Q4至G6 的反馈信号将这两个门打开,因此可接收输入信号D, ![]()

![]() 。

。

(2)当CP由0变1时,即上升沿到来:G3 和G4打开,它们的输出Q3和Q4的状态由 G5和G6的输出状态决定。 ![]() ,

, ![]() 。由基本RS触发器的逻辑功能,可知Q=D.

。由基本RS触发器的逻辑功能,可知Q=D.

(3)触发器翻转后,在CP=1时输入信号被封锁。G3和G4打开后,他们的输出Q3 和Q4 的状态时互补的,即必定有一个是0,若Q3=0,则经G3输出至G5 输入的反馈线将G5封锁,即封锁了D通往基本RS触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。Q4=0 时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。Q4输出至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3 输入的反馈线起到了阻止触发器置0的作用,称为置0阻塞线。因此该触发器称为维持-阻塞触发器。

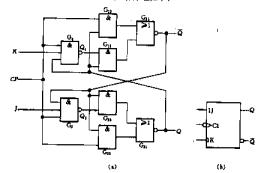

2. 利用传输延迟时间的边沿触发器

利用传输延迟时间的边沿触发器

这个电路包含一个由与或非门G1和G2组成的基本RS触发器和两个输入控制门G3和G4。而且,门G3和G4传输延迟时间大于基本RS触发器的翻转时间。

设触发器的初始状态为 ![]() ,

, ![]() 。

。

Ⅰ. ![]() 时,门B、B’和G3、G4被CP的低电平封锁,而G3、G4的输出P、P’均为高电平,

时,门B、B’和G3、G4被CP的低电平封锁,而G3、G4的输出P、P’均为高电平,

门A、A’是打开的,所以基本RS触发器的状态通过A、A’得以保持。

Ⅱ.CP变为高电平以后,门B、B’首先解除封锁,基本RS触发器可以通过B、B’继续保持原

状态不变。此时输入为 ![]() 、

、 ![]() ,则经过门G3、G4的传输延迟时间后

,则经过门G3、G4的传输延迟时间后 ![]() 、

、 ![]() ,门

,门

A、A’均不导通,对基本RS触发器的状态没有影响。

Ⅲ.当CP下降沿到达时,门B、B’立即封锁,但由于门G3、G4存在传输延迟时间,所以P、P’

的电平不会马上改变。因此,在瞬间出现A、B各有一个输入端为低电平的状态,使 ![]() ,

,

并经过门A’使 ![]() 。由于G3的传输延迟时间足够长,可以保证在P点的低电平消失之前

。由于G3的传输延迟时间足够长,可以保证在P点的低电平消失之前 ![]() 的

的

低电平已反馈到了门A,所以在P点的低电平消失以后触发器获得的1状态仍将保持下去。

经过门G3、G4的传输延迟时间以后,P、P’都变为高电平,但对基本RS触发器状态并无影响。而CP的低电平已将门G3、G4封锁,J、K状态即使再发生变化也不会影响触发器的状态了。

边沿触发器的特点

不论是维阻型D边沿触发器还是利用传输延迟时间的JK边沿触发器,它们共同的动作特点就是触发器的次态仅取决于CP信号的上升沿或下降沿到达时输入的逻辑状态,而在这之前或之后,输入信号的变化对触发器输出的状态没有影响。这一特点有效的提高了触发器的抗干扰能力,因而也提高了电路的工作可靠性。