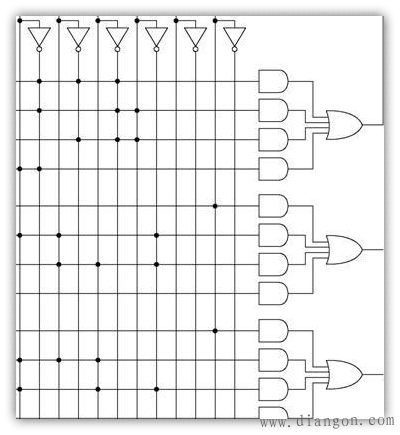

输出和反馈结构由可编程的与阵列和固定的或阵列组成,没有输出反馈信号,输入和输出引出端是固定的,不能由用户自行定义。只适用于简单的组合逻辑电路设计。

1.输入和输出型结构

具有三态输出缓冲器和反馈缓冲器。反馈缓冲器可使三态输出反馈到与阵列输入端,构成简单的触发器,使输出具有记忆功能。用户通过编程可以控制三态输出缓冲器的状态,从而实现对输入/输出引出端数目的任意配置。利用可编程输入/输型PAL器件,可设计编码器、译码器、数据选择器等组合逻辑电路,也可完成串行数据移位和循环等操作。

2.带反馈的寄存器型结构

具有记忆功能,由于整个器件只有一个共用时钟和一个输出使能输入端,因此可以构成计数器等同步时序逻辑电路。

3.带异或的寄存器型结构

与阵列的输出分成两组相或,经异或运算后加到D触发器的输入端,使得逻辑电路的设计更加灵活、方便。

4.算术选通反馈型结构

在异或型PAL的基础上增加算术选通电路,产生输入信号和反馈信号的4个最大项。算术选通电路产生的4个最大项,加到与阵列输入端,通过对与阵列编程,可得到16种逻辑组合输出。

算术选通反馈型PAL器件,主要用于实现快速的加、减、大于、小于等算术逻辑电路。

5.乘积项公用输出结构

相邻两个逻辑单元乘积项可同时接到两个或门。

6.宏单元输出结构

PAL22V10的宏单元由一个触发器和两个可编程多路选择器组成,通过对两个多路选择器进行编程,每个宏单元可以设置4种输出结构形式和两种反馈信号,因而具有更强的通用性和灵活性。

应用

PAL器件速度快,功耗低,并有多种结构类型,可用来设计各种组合逻辑电路和时序逻辑电路。设计时主要考虑以下几个方面:

PAL器件速度快,功耗低,并有多种结构类型,可用来设计各种组合逻辑电路和时序逻辑电路。设计时主要考虑以下几个方面:

(1) 一个PAL器件的输入/输出引出端总数是有限的。

(2) 每个PAL器件输出乘积项数目是有限的。

(3) 在具有寄存器和宏单元结构的PAL器件中,当逻辑单元中的寄存器作为内部反馈寄存器使用时,需占用一个逻辑单元,则对应的输出引出端不能再作它用;当逻辑单元作为组合输出时,也占用一个逻辑单元,其内部寄存器也不能使用。