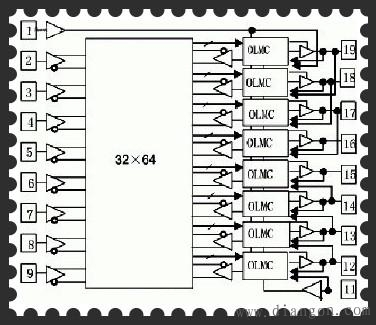

GAL有五个部分组成:

1. 输入端:GAL16V8的2~9脚共8个输入端,每个输入端有一个缓冲器,并由缓冲器引出两个互补的输出到与阵列;

2. 与阵列部分:它由8根输入及8根输出各引出两根互补的输出构成32列,即与项的变量个数为16;8根输出每个输出对应于一个8输入或门(相当于每个输出包含8个与项)构成64行,即GAL16V8的与阵列为一个32×64的阵列,共2048个可编程单元(或结点);

3. 输出宏单元:GAL16V8共有8个输出宏单元,分别对应于12~19脚。每个宏单元的电路可以通过编程实现所有PAL输出结构实现的功能;

4. 系统时钟:GAL16V8的1脚为系统时钟输入端,与每个输出宏单元中D触发器时钟输入端相连,可见GAL器件只能实现同步时序电路,而无法实现异步的时序电路;

5. 输出三态控制端:GAL16V8的11脚为器件的三态控制公共端。