有源晶振

有源晶振通常的用法:一脚悬空,二脚接地,三脚接输出,四脚接电压。

有源晶振不需要DSP的内部振荡器,信号质量好,比较稳定,而且连接方式相对简单(主要是做好电源滤波,通常使用一个电容和电感构成的PI型滤波网络,输出 端用一个小阻值的电阻过滤信号即可),不需要复杂的配置电路。相对于无源晶体,有源晶振的缺陷是其信号电平是固定的,需要选择好合适输出电平,灵活性较 差,而且价格高。

有源晶振是右石英晶体组成的,石英晶片之所以能当为振荡器使用,是基于它的压电效应:在晶片的两个极上加一电场,会使晶体产生机械变形;在石英晶片上加上 交 变电压,晶体就会产生机械振动,同时机械变形振动又会产生交变电场,虽然这种交变电场的电压极其微弱,但其振动频率是十分稳定的。当外加交变电压的频率与 晶片的固有频率(由晶片的尺寸和形状决定)相等时,机械振动的幅度将急剧增加,这种现象称为“压电谐振”。

压电谐振状态的建立和维持都必须借助于振荡器电路才能实现。图3是一个串联型振荡器,晶体管T1和T2构成的两级放大器,石英晶体XT与电容C2构成LC 电 路。在这个电路中,石英晶体相当于一个电感,C2为可变电容器,调节其容量即可使电路进入谐振状态。该振荡器供电电压为5V,输出波形为方波。

单片机的内部时钟与外部时钟

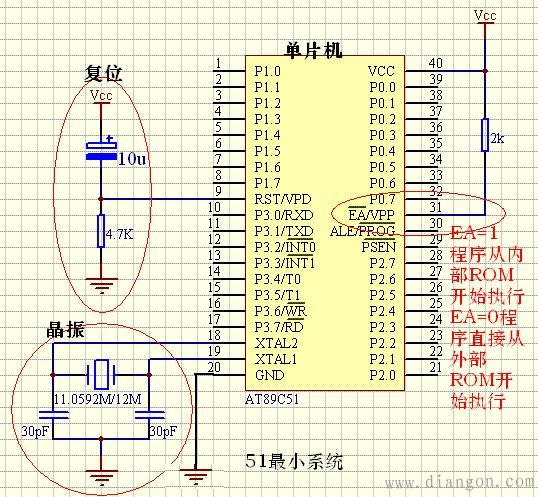

单片机有内部时钟方式和外部时钟方式两种:(1)单片机的XTAL1和XTAL2内部有一片内振荡器结构,但仍需要在XTAL1和XTAL2两端连接一个晶振和两个电容才能组成时钟电路,这种使用晶振配合产生信号的方法是内部时钟方式;(2)单片机还可以工作在外部时钟方式下,外部时钟方式较为简单,可直接向单片机XTAL1引脚输入时钟信号方波,而XTAL2管脚悬空。 既然外部时钟方式相对内部较为方便,那为什么大多数单片机系统还是选择内部时钟方式呢?这是因为单片机的内部振荡器能与晶振、电容构成一个性能非常好的时钟信号源,而如果要产生这样的信号作为外部时钟信号输入到单片机中,则需要添加的器件远不止一个晶振和两个电容这么简单。时钟电路在单片机系统中很重要,它能控制着单片机工作的节奏,是必不可少的部分。

晶振电路

晶振是晶体振荡器的简称,在电气上它可以等效成一个电容和一个电阻并联再串联一个电容的二端网络。电工学上这个网络有两个谐振点,以频率的高低分,其中较低的频率是串联谐振;较高的频率是并联谐振。由于晶体自身的特性致使这两个频率的距离相当的接近,在这个极窄的频率范围内,晶振等效为一个电感,所以只要晶振的两端并联上合适的电容它就会组成并联谐振电路。这个并联谐振电路加到一个负反馈电路中就可以构成正弦波振荡电路,由于晶振等效为电感的频率范围很窄,所以即使其他元件的参数变化很大,这个振荡器的频率也不会有很大的变化。

晶振有一个重要的参数——负载电容值,选择与负载电容值相等的并联电容,就可以得到晶振标称的谐振频率。一般的晶振振荡电路都是在一个反相放大器(注意是放大器不是反相器)的两端接入晶振,再有两个电容分别接到晶振的两端,每个电容的另一端再接到地,这两个电容串联的容量值就应该等于负载电容。请注意一般IC的引脚都有等效输入电容,这个不能忽略。一般的晶振的负载电容为15pF或12.5pF,如果再考虑元件引脚的等效输入电容,则两个22pF的电容构成晶振的振荡电路就是比较好的选择。

如上图:晶振是给单片机提供工作信号脉冲的 这个脉冲就是单片机的工作速度 比如 12M晶振 单片机工作速度就是每秒12M 当然 单片机的工作频率是有范围的不能太大 一般24M就不上去了 不然不稳定。

晶振与单片机的脚XTAL0和脚XTAL1构成的振荡电路中会产生偕波(也就是不希望存在的其他频率的波) 这个波对电路的影响不大 但会降低电路的时钟振荡器的稳定性 为了电路的稳定性起见 ATMEL公司只是建议在晶振的两引脚处接入两个10pf-50pf的瓷片电容接地来削减偕波对电路的稳定性的影响 所以晶振所配的电容在10pf-50pf之间都可以的 没有什么计算公式。

晶振电路中如何选择电容C1,C2?

(1)因为每一种晶振都有各自的特性,所以最好按制造厂商所提供的数值选择外部元器件。

(2)在许可范围内,C1,C2值越低越好。C值偏大虽有利于振荡器的稳定,但将会增加起振时间。

(3)应使C2值大于C1值,这样可使上电时,加快晶振起振。

在石英晶体谐振器和陶瓷谐振器的应用中,需要注意负载电容的选择。不同厂家生产的石英晶体谐振器和陶瓷谐振器的特性和品质都存在较大差异,在选用,要了解该型号振荡器的关键指标,如等效电阻,厂家建议负载电容,频率偏差等。在实际电路中,也可以通过示波器观察振荡波形来判断振荡器是否工作在最佳状态。示波器在观察振荡波形时,观察OSCO管脚(Oscillator output),应选择100MHz带宽以上的示波器探头,这种探头的输入阻抗高,容抗小,对振荡波形相对影响小。(由于探头上一般存在10~20pF的电容,所以观测时,适当减小在OSCO管脚的电容可以获得更接近实际的振荡波形)。工作良好的振荡波形应该是一个漂亮的正弦波,峰峰值应该大于电源电压的70%。若峰峰值小于70%,可适当减小OSCI及OSCO管脚上的外接负载电容。反之,若峰峰值接近电源电压且振荡波形发生畸变,则可适当增加负载电容。

用示波器检测OSCI(Oscillator input)管脚,如何解决容易导致振荡器停振的问题?

部分的探头阻抗小不可以直接测试,可以用串电容的方法来进行测试。如常用的4MHz石英晶体谐振器,通常厂家建议的外接负载电容为10~30pF左右。若取中心值15pF,则C1,C2各取30pF可得到其串联等效电容值15pF。同时考虑到还另外存在的电路板分布电容,芯片管脚电容,晶体自身寄生电容等都会影响总电容值,故实际配置C1,C2时,可各取20~15pF左右。并且C1,C2使用瓷片电容为佳。

如何判断电路中晶振是否被过分驱动?

电阻RS常用来防止晶振被过分驱动。过分驱动晶振会渐渐损耗减少晶振的接触电镀,这将引起频率的上升。可用一台示波器检测OSC输出脚,如果检测一非常清晰的正弦波,且正弦波的上限值和下限值都符合时钟输入需要,则晶振未被过分驱动;相反,如果正弦波形的波峰,波谷两端被削平,而使波形成为方形,则晶振被过分驱动。这时就需要用电阻RS来防止晶振被过分驱动。判断电阻RS值大小的最简单的方法就是串联一个5k或10k的微调电阻,从0开始慢慢调高,一直到正弦波不再被削平为止。通过此办法就可以找到最接近的电阻RS值。