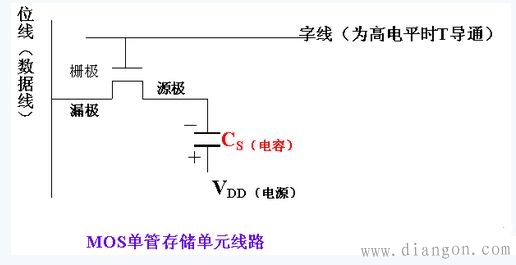

(1)动态存储器的组成:由单个MOS管来存储一位二进制信息。信息存储在MOS管的源极的寄生电容CS中。

◎写数据时:字线为高电平,T导通。

写“1”时,位线(数据线)为低电平, VDD(电源)将向电容充电

写“0时,位线(数据线)为高电平, 若电容存储了电荷,则将会使电容完成放电,就表示存储了“0”。

◎ 读数据时:先使位线(数据线)变为高电平,当字线高电平到来时T导通,若电容原存储有电荷( 是“1” ),则电容就要放电,就会使数据线电位由高变低;若电容没有存储电荷( 是“0” ),则数据线电位不会变化。检测数据线上电位的变化就可以区分读出的数据是1还是0。

注意

①读操作使电容原存储的电荷丢失,因此是破坏性读出。为保持原记忆内容,必须在读操作后立刻跟随一次写入操作,称为预充电延迟。

②向动态存储器的存储单元提供地址,是先送行地址再送列地址。原因就是对动态存储器必须定时刷新(如2ms),刷新不是按字处理,而是每次刷新一行,即为连接在同一行上所有存储单元的电容补充一次能量。

③在动态存储器的位线上读出信号很小,必须接读出放大器,通常用触发器线路实现。

④存储器芯片内部的行地址和列地址锁存器分先后接受行、列地址。

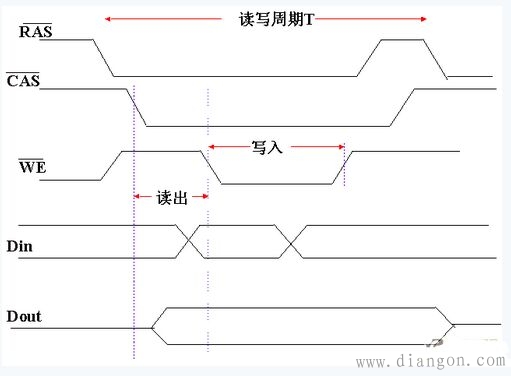

⑤RAS、CAS、WE、Din、Dout时序关系如下图: