1、输出结构

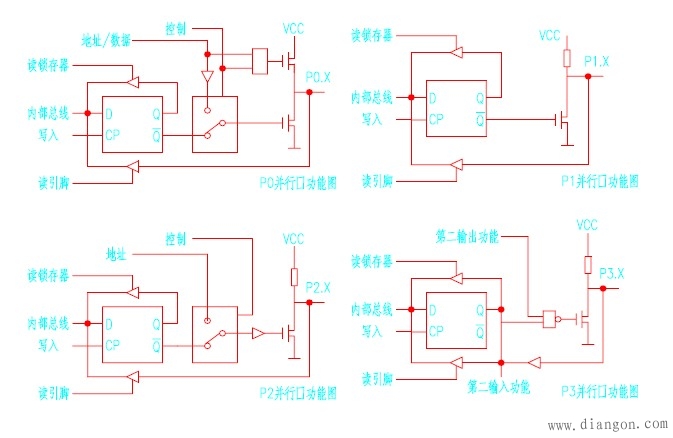

<并行口结构图>

先看P1口的一位的结构示意图(只画出了输出部份):从图中能看出,开关的打开和合上代表了管脚输出的高和低,如果开关合上了,则管脚输出就是低,如果开关打开了,则输出高电平,这个开关是由一根线来控制的,这根数据总线是出自于CPU,让我们回想一下,数据总线是一根大家公用的线,很多的器件和它连在一起,在不一样的时候,不一样的器件当然需要不一样的信号,如某一时刻我们让这个管脚输出高电平,并要求保持若干时间,在这段时间里,计算机当然在忙个不停,在与其它器件进行联络,这根控制线上的电平未必能保持原来的值不变,输出就会发生变化了。怎么解决这个问题呢?我们在存储器一节中学过,存储器中是能存放电荷的,我们不妨也加一个小的存储器的单元,并在它的前面加一个开关,要让这一位输出时,就把开关打开,信号就进入存储器的单元,然后马上关闭开关,这样这一位的状态就被保存下来,直到下一次命令让它把开关再打开为止。这样就能使这一位的状态与别的器件无关了,这么一个小单元,我们给它一个很形象的名字,称之为“锁存器”。

2、输入结构

这是并行口的一位的输出结构示意图,再看,除了输出之外,还有两根线,一根从外部管脚接入,另一根从锁存器的输出接出,分别标明读管脚和读锁存器。这两根线是用于从外部接收信号的,为什么要两根呢?原来,在51单片机中输入有两种方式,分别称为‘读管脚’和‘读锁存器’,第一种方式是将管脚作为输入,那是真正地从外部管脚读进输入的值,第二种方式是该管脚处于输出状态时,有时需要改变这一位的状态,则并不需要真正地读管脚状态,而只是读入锁存器的状态,然后作某种变换后再输出。

请注意输入结构图,如果将这一根引线作为输入口使用,我们并不能保证在任何时刻都能得到正确的结果(为什么?)参考图2输入示意图。接在外部的开关如果打开,则应当是输入1,而如果闭合开关,则输入0,但是,如果单片机内部的开关是闭合的,那么不管外部的开关是开还是闭,单片机接受到的数据都是0。可见,要让这一端口作为输入使用,要先做一个‘准备工作’,就是先让内部的开关断开,也就是让端口输出‘1’才行。正因为要先做这么一个准备工作,所以我们称之为“准双向I/O口”。

以上是P1口的一位的结构,P1口其它各位的结构与之相同,而其它三个口:P0、P2、P3则除入作为输入输出口之外还有其它用途,所以结构要稍复杂一些,但其用于输入、输出的结构是相同的。看图()。对我们来说,这些附加的功能不必由我们来控制,所以我们就不去关心它了。