1、锁存器Latch 和 触发器flipflop

锁存器能根据输入端把结果自行保持;触发器是指由时钟边沿触发的存储器单元;

由敏感信号(电平,边沿)控制的锁存器就是触发器;

2、写电路时,产生锁存器的原因

if语句中,没有写else,默认保持原值,产生锁存器,可能不是想要的结果;

case语句中,没有写完整default项,也容易产生锁存器;

例子:

always@(a or b)

begin

if(a) q=b;

end

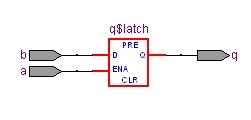

产生了锁存器,如下

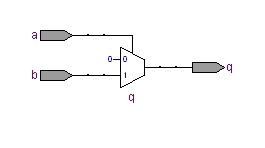

没有锁存器的情况

always@(a or b)

begin

if(a) q=b;

else q=0;

end

3、避免使用D锁存器,尽量使用D触发器

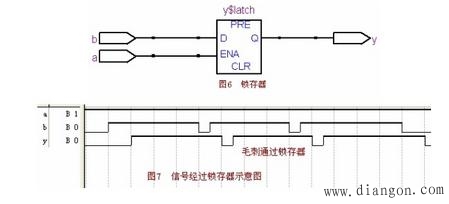

D锁存器

moduletest_latch(y,a,b);

outputy;inputa;inputb;regy;

always@(aorb)begin

if(a==1’b1)

y=b;endendmodule

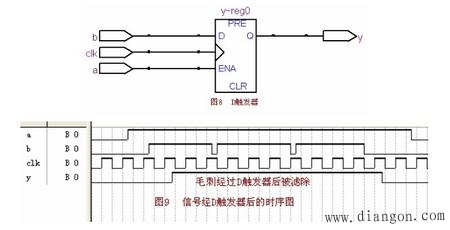

D触发器

moduletest_d(y,clk,a,b);

outputy;inputclk;inputa;inputb;regy;

always@(posedgeclk)begin

if(a==1'b1)

y=b;

endendmodule

从图8可知,例10对应的电路是D触发器。信号a被综合成D触发器的使能端,只有在时钟上沿到来且a为高时,b信号的值才能传递给a;只要在时钟上升沿期间信号b是稳定,即使在其他时候b还有毛刺,经过D触发器后数据是稳定的,毛刺被滤除。